【導(dǎo)讀】有限脈沖響應(yīng)(FIR)和無限脈沖響應(yīng)(IIR)濾波器都是常用的數(shù)字信號處理算法---尤其適用于音頻處理應(yīng)用。因此�����,在典型的音頻系統(tǒng)中�,處理器內(nèi)核的很大一部分時間用于FIR和IIR濾波�。數(shù)字信號處理器上的片內(nèi)FIR和IIR硬件加速器也分別稱為FIRA和IIRA�,我們可以利用這些硬件加速器來分擔(dān)FIR和IIR處理任務(wù),讓內(nèi)核去執(zhí)行其他處理任務(wù)�。在本文中,我們將借助不同的使用模型以及實(shí)時測試示例來探討如何在實(shí)踐中利用這些加速器�����。

簡介

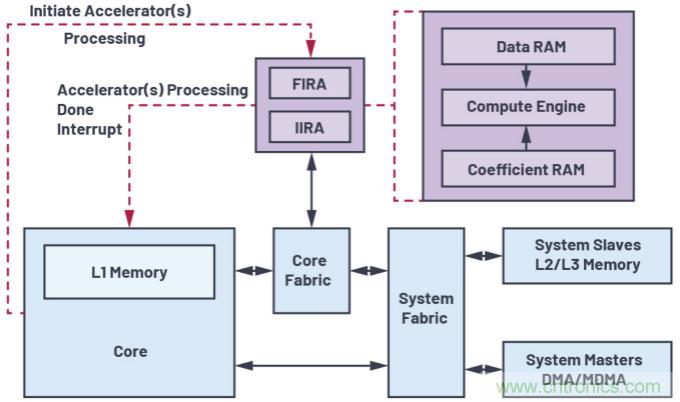

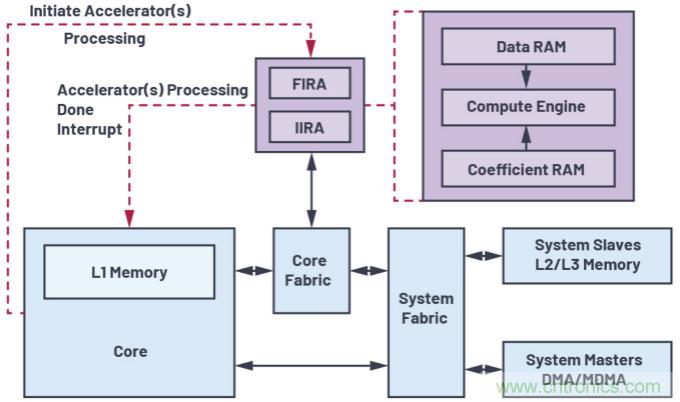

圖1.FIRA和IIRA系統(tǒng)方框圖

圖1顯示了FIRA和IIRA的簡化方框圖��,以及它們與其余處理器系統(tǒng)和資源的交互方式����。

?

● FIRA和IIRA模塊均主要包含一個計(jì)算引擎(乘累加(MAC)單元)以及一個小的本地數(shù)據(jù)和系數(shù)RAM。

?

● 為開始進(jìn)行FIRA/IIRA處理�����,內(nèi)核使用通道特定信息初始化處理器存儲器中的DMA傳輸控制塊(TCB)鏈���。然后將該TCB鏈的起始地址寫入FIRA/IIRA鏈指針寄存器����,隨后配置FIRA/IIRA控制寄存器以啟動加速器處理。一旦所有通道的配置完成����,就會向內(nèi)核發(fā)送一個中斷,以便內(nèi)核將處理后的輸出用于后續(xù)操作��。

?

● 從理論上講���,最好的方法是將所有FIR和/或IIR任務(wù)從內(nèi)核轉(zhuǎn)移給加速器�,并允許內(nèi)核同時執(zhí)行其他操作����。但在實(shí)踐中,這并非始終可行���,特別是當(dāng)內(nèi)核需要使用加速器輸出進(jìn)一步處理���,并且沒有其他獨(dú)立的任務(wù)需要同時完成時。在這種情況下��,我們需要選擇合適的加速器使用模型來達(dá)到最佳效果���。

在本文中,我們將討論針對不同應(yīng)用場景充分利用這些加速器的各種模型��。

實(shí)時使用FIRA和IIRA

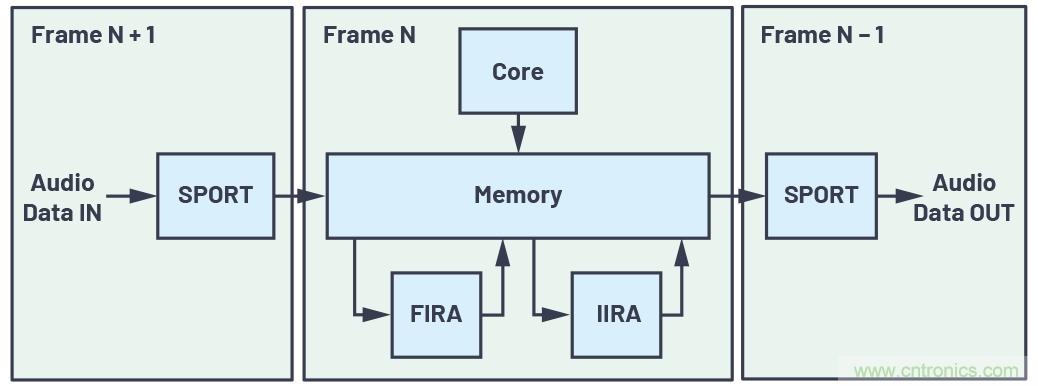

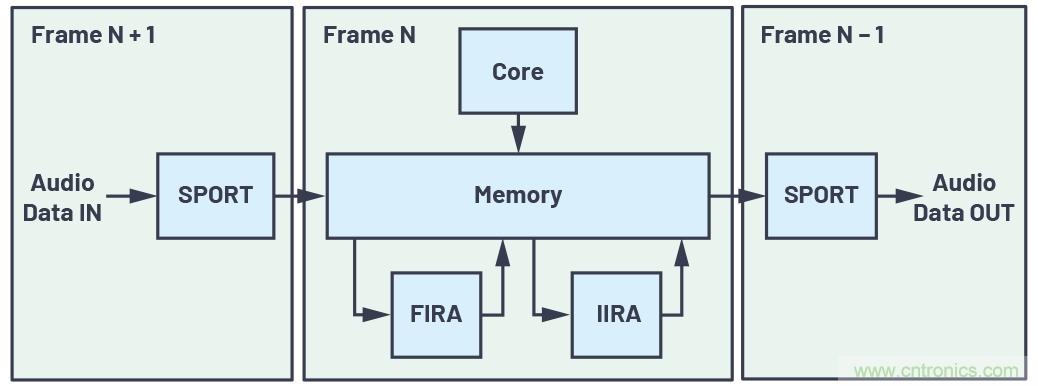

圖2.典型實(shí)時音頻數(shù)據(jù)流

圖2顯示了典型實(shí)時PCM音頻數(shù)據(jù)流圖。一幀數(shù)字化PCM音頻數(shù)據(jù)通過同步串行端口(SPORT)接收�����,并通過直接存儲器訪問(DMA)發(fā)送至存儲器���。在繼續(xù)接收幀N+1時��,幀N由內(nèi)核和/或加速器處理����,之前處理的幀(N-1)的輸出通過SPORT發(fā)送至DAC進(jìn)行數(shù)模轉(zhuǎn)換�����。

加速器使用模型

如前所述�����,根據(jù)應(yīng)用的不同����,可能需要以不同的方式使用加速器,以最大限度分擔(dān)FIR和/或IIR處理任務(wù),并盡可能節(jié)省內(nèi)核周期以用于其他操作���。從高層次角度來看���,加速器使用模型可分為三類:直接替代、拆分任務(wù)和數(shù)據(jù)流水線�����。

直接替代

● 內(nèi)核FIR和/或IIR處理直接被加速器替代����,內(nèi)核只需等待加速器完成此任務(wù)。

● 此模型僅在加速器的處理速度比內(nèi)核快時才有效��;即��,使用FIRA模塊����。

拆分任務(wù)

?

● FIR和/或IIR處理任務(wù)在內(nèi)核和加速器之間分配。

?● 當(dāng)多個通道可并行處理時���,此模型特別有用�。

?● 根據(jù)粗略的時序估算,在內(nèi)核和加速器之間分配通道總數(shù)��,使二者大致能夠同時完成任務(wù)���。

?● 如圖3所示,與直接替代模型相比�����,此使用模型可節(jié)省更多的內(nèi)核周期���。

數(shù)據(jù)流水線

● 內(nèi)核和加速器之間的數(shù)據(jù)流可進(jìn)行流水線處理����,使二者能夠在不同數(shù)據(jù)幀上并行處理�����。

● 如圖3所示����,內(nèi)核處理第N個幀,然后啟動加速器對該幀進(jìn)行處理�。內(nèi)核隨后繼續(xù)進(jìn)一步并行處理加速器在上一迭代中產(chǎn)生的第N-1幀的輸出����。該序列允許將FIR和/或IIR處理任務(wù)完全轉(zhuǎn)移給加速器����,但輸出會有一些延遲。

● 流水線級以及輸出延遲都可能會增加�,具體取決于完整處理鏈中此類FIR和/或IIR處理級的數(shù)量。

圖3說明了音頻數(shù)據(jù)幀如何在不同加速器使用模型的三個階段之間傳輸---DMA IN����、內(nèi)核/加速器處理和DMA OUT。它還顯示了通過采用不同的加速器使用模型將FIR/IIR全部或部分處理轉(zhuǎn)移到加速器上�����,與僅使用內(nèi)核模型相比����,內(nèi)核空閑周期如何增加。

圖3.加速器使用模型比較

SHARC處理器上的FIRA和IIRA

以下ADI SHARC®處理器系列支持片內(nèi)FIRA和IIRA(從舊到新)�。

?

● ADSP-214xx (例如, ADSP-21489)

● ADSP-SC58x

● ADSP-SC57x/ADSP-2157x

● ADSP-2156x

這些處理器系列:

?

● 計(jì)算速度不同

● 基本編程模型保持不變���,ADSP-2156x處理器上的自動配置模式(ACM)除外����。

● FIRA有四個MAC單元,而IIRA只有一個MAC單元��。

ADSP-2156x處理器上的FIRA/IIRA改進(jìn)

ADSP-2156x是SHARC處理器系列中的最新的產(chǎn)品�����。它是第一款單核1 GHz SHARC處理器�����,其FIRA和IIRA也可在1 GHz下運(yùn)行����。ADSP-2156x處理器上的FIRA和IIRA與其前代ADSP-SC58x/ADSP-SC57x處理器相比�����,具有多項(xiàng)改進(jìn)�����。

性能改進(jìn)

?

● 計(jì)算速度提高了8倍(從SCLK-125 MHz至CCLK-1 GHz)��。

● 由于內(nèi)核和加速器借助專用內(nèi)核結(jié)構(gòu)實(shí)現(xiàn)了更緊密的集成,因此減少了內(nèi)核和加速器之間的數(shù)據(jù)和MMR訪問延遲�。

功能改進(jìn)

添加了ACM支持,以盡量減少進(jìn)行加速器處理所需的內(nèi)核干預(yù)�����。此模式主要具有以下新特性:

?

● 允許加速器暫停以進(jìn)行動態(tài)任務(wù)排隊(duì)�����。

● 無通道數(shù)限制�����。

● 支持觸發(fā)生成(主器件)和觸發(fā)等待(從器件)��。

● 為每個通道生成選擇性中斷���。

實(shí)驗(yàn)結(jié)果

在本節(jié)中��,我們將討論在ADSP-2156x評估板上���,借助不同的加速器使用模型實(shí)施兩個實(shí)時多通道FIR/IIR用例的結(jié)果

用例1

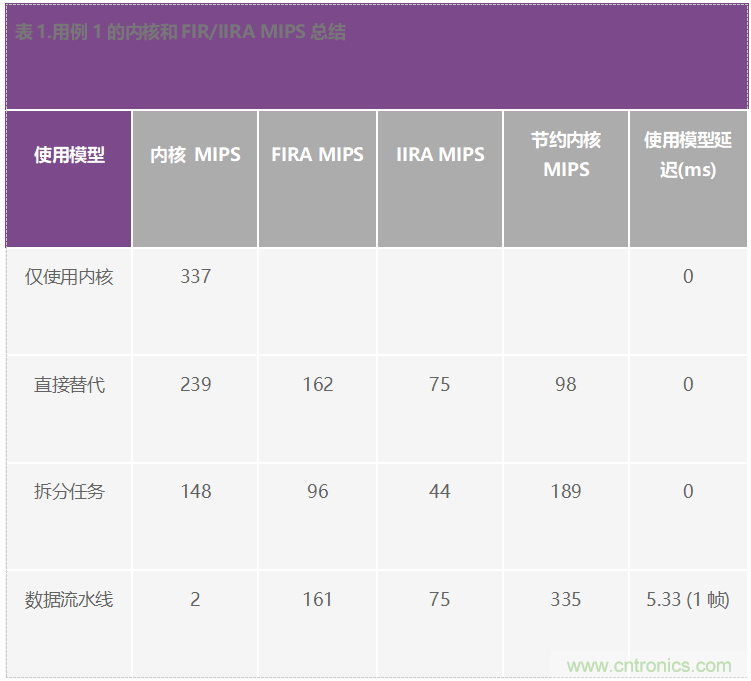

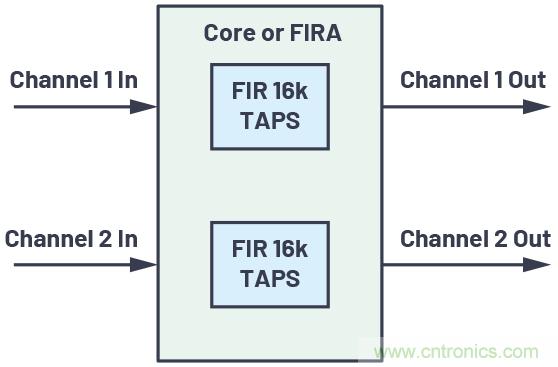

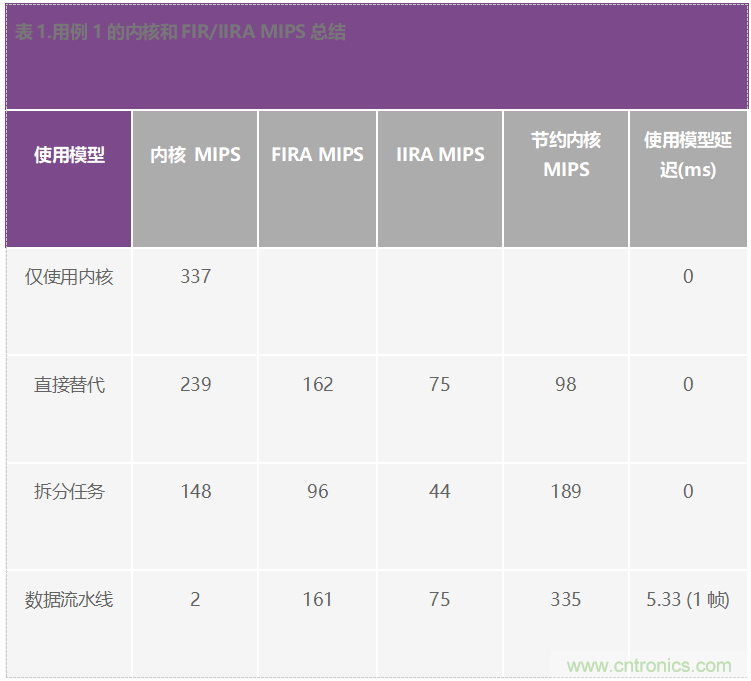

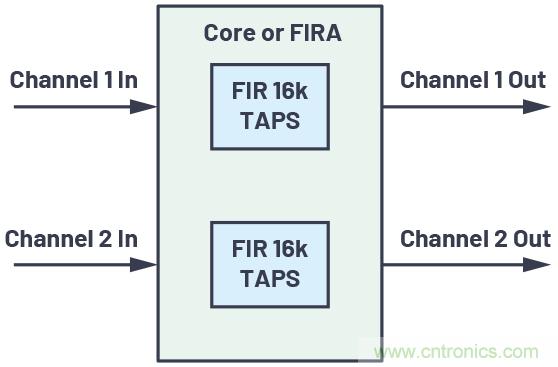

圖4顯示用例1的方框圖。采樣率為48 kHz���,模塊大小為256個采樣點(diǎn)�����,拆分任務(wù)模型中使用的內(nèi)核與加速器通道比為5:7����。

表1顯示測得的內(nèi)核和FIRA MIPS數(shù)量,以及與僅使用內(nèi)核模型相比獲得的節(jié)約內(nèi)核MIPS結(jié)果���。表中還顯示了相應(yīng)使用模型增加的額外輸出延遲。正如我們所看到的����,使用加速器配合數(shù)據(jù)流水線使用模型,可節(jié)約高達(dá)335內(nèi)核MIPS���,但導(dǎo)致1塊(5.33 ms)的輸出延遲���。直接替代和拆分任務(wù)使用模型也分別可節(jié)約98 MIPS和189 MIPS,而且未導(dǎo)致任何額外的輸出延遲�����。

圖4.用例1方框圖

表1.用例1的內(nèi)核和FIR/IIRA MIPS總結(jié)

用例2

圖5顯示用例2的方框圖。采樣率為48 kHz���,模塊大小為128個采樣點(diǎn)���,拆分任務(wù)模型中使用的內(nèi)核與加速器通道比為1:1。

與表1一樣�,表2也顯示了此用例的結(jié)果。正如我們所看到的�����,使用加速器配合數(shù)據(jù)流水線使用模型����,可節(jié)約高達(dá)490內(nèi)核MIPS,但導(dǎo)致1模塊(2.67 ms)的輸出延遲���。拆分任務(wù)使用模型可節(jié)約234內(nèi)核MIPS�����,而沒有導(dǎo)致任何額外輸出延遲���。請注意���,與用例1中不同,在用例2中內(nèi)核使用頻域(快速卷積)處理����,而非時域處理。這就是為何處理一個通道所需的內(nèi)核MIPS比FIRA MIPS少的原因���,這可導(dǎo)致直接替代使用模型實(shí)現(xiàn)負(fù)的內(nèi)核MIPS節(jié)約����。

圖5.用例2方框圖

表2.用例2的內(nèi)核和FIR/IIRA MIPS總結(jié)

結(jié)論

在本文中���,我們看到如何利用不同的加速器使用模型實(shí)現(xiàn)所需的MIPS和處理目標(biāo),從而將大量內(nèi)核MIPS轉(zhuǎn)移到ADSP-2156x處理器上的FIRA和IIRA加速器����。

進(jìn)一步閱讀

Nayak, Sanket和Mitesh Moonat�����。 “工程師對話筆記EE-408:使用ADSP-2156x高性能FIR/IIR加速器。”ADI公司���,2019年8月���。

作者

Mitesh Moonat

Mitesh Moonat目前在印度班加羅爾(ADBL)處理器應(yīng)用團(tuán)隊(duì)擔(dān)任應(yīng)用工程師。他從事前/后晶片驗(yàn)證�、外設(shè)驅(qū)動器開發(fā)和SHARC處理器支持工作。在ADI就職期間�����,他還從事Blackfin和21xx處理器工作���。他的工作領(lǐng)域包括處理器架構(gòu)���、數(shù)字信號處理算法優(yōu)化、模塊以及嵌入式系統(tǒng)的系統(tǒng)級調(diào)試����。Mitesh于2006年加入ADI公司。他畢業(yè)于印度瓦朗加爾國家技術(shù)學(xué)院���,獲得電子和通信工程學(xué)士學(xué)位�。

Sanket Nayak

Sanket Nayak是印度班加羅爾(ADBL)處理器應(yīng)用團(tuán)隊(duì)的產(chǎn)品應(yīng)用工程師。他于2016年加入ADI公司���,一直從事汽車DSP的前/后晶片驗(yàn)證���、驅(qū)動器/FuSa ROM設(shè)計(jì)、開發(fā)和測試工作����。他獲得班加羅爾PES技術(shù)學(xué)院電子和通信工程學(xué)士學(xué)位。

推薦閱讀: