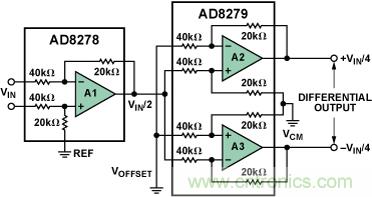

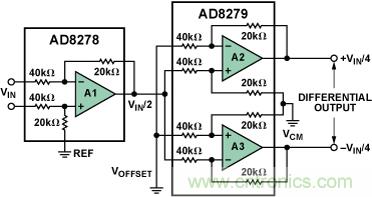

【導(dǎo)讀】采用小尺寸工藝設(shè)計(jì)的高性能ADC通常采用1.8V至5V單電源或±5V雙電源供電��。為了處理±10 V或更大的實(shí)際信號(hào)���,ADC一般前置一個(gè)放大器以衰減該信號(hào),防止ADC輸入端出現(xiàn)飽和或受損�。這種放大器通常具有單端輸出,但為了獲得差分輸入ADC的全部?jī)?yōu)勢(shì)�����,包括更高動(dòng)態(tài)范圍����、更佳共模抑制性能和更低的噪聲敏感度,具有差分輸出會(huì)更有利�。圖1顯示一個(gè)增益為1/2的差分輸出放大器系統(tǒng)。

圖1. G = 1/2的差分輸出差動(dòng)放大器功能框圖

差分放大器A1的增益配置為1/2����。 此放大器的輸出送到放大器A2的同相輸入端和放大器A3的反相輸入端。放大器A2和A3也以增益1/2工作�����,二者的輸出180度反相�,構(gòu)成一路差分輸出。差分輸出電壓VOUT A2 – VOUT A3等于 VIN/4 – (–VIN/4), 或者 VIN/2的總差分輸出電壓���,正如希望的那樣���。

VOFFSET引腳可用來偏移輸出從而提高ADC的動(dòng)態(tài)范圍。從VOFFSET到輸出端的差分增益為–1�。如果不需要偏移調(diào)整,應(yīng)將此節(jié)點(diǎn)接地��。

VCM引腳設(shè)置差分輸出的共模電壓��。這在驅(qū)動(dòng)單電源ADC時(shí)特別有用����,可以將電路的共模輸出設(shè)置到中間電源電壓�。從 VCM到輸出端的增益為1����。如果不需要共模調(diào)整,應(yīng)將此節(jié)點(diǎn)接地���。

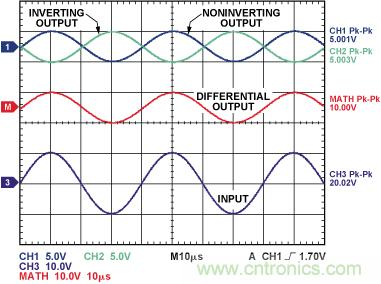

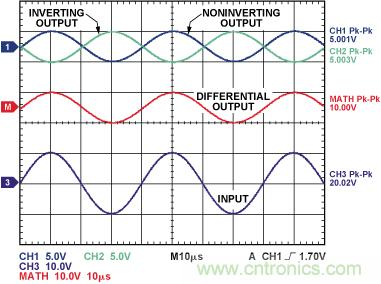

圖2顯示該電路的性能�。輸入為25kHz��、20V峰峰值正弦波�。通道1為同相輸出,通道2為反相輸出���,通道3為輸入�。Math通道為兩路輸出之差���。每路輸出均為輸入信號(hào)的1/4�,兩路輸出彼此反相����,因此其差值為輸入信號(hào)的1/2。

圖2. 差分輸出為輸入信號(hào)的1/2

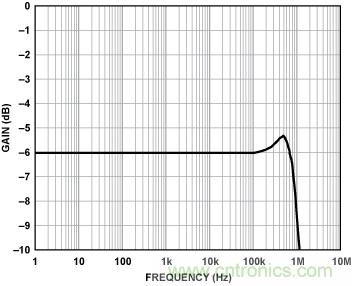

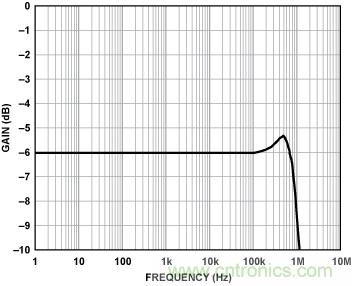

圖3顯示該電路增益與頻率響應(yīng)的關(guān)系,證明它很穩(wěn)定���,在1MHz帶寬內(nèi)的峰化小于1dB����。

圖3. 差分輸出差動(dòng)放大器的頻率響應(yīng)

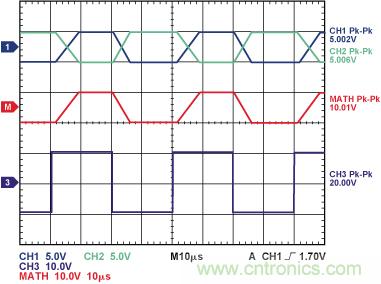

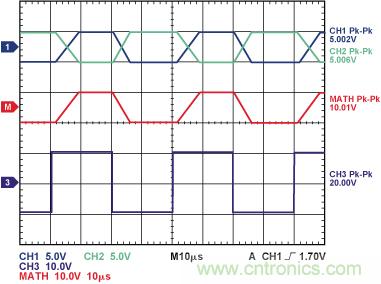

圖4表明����,該電路對(duì)大方波輸入的響應(yīng)沒有可觀的過沖����,建立時(shí)間非常快��。因?yàn)楦鞣糯笃鲀H攜帶一半的信號(hào)�,所以差分輸出壓擺率是單個(gè)輸出的兩倍。

圖4. 差分輸出差動(dòng)放大器的大信號(hào)性能

雙通道差動(dòng)放大器AD82791采用14引腳窄體SOIC封裝�。AD82782采用8引腳MSOP封裝。經(jīng)過激光調(diào)整的精密電阻集成在放大器的同一芯片上�,因此其失調(diào)、增益��、共模誤差和溫度漂移非常小��,構(gòu)成一個(gè)高精度系統(tǒng)����。雖然AD8278 (200 μA)和AD8279(每個(gè)放大器200 μA)的功耗很低�����,但該系統(tǒng)具有1MHz的帶寬和2.4V/μs的壓擺率���。AD8278和AD8279可以在2.5V單電源至±18V雙電源的極寬電源電壓范圍內(nèi)工作。輸入擺幅可以大大超出電源軌��,因而該系統(tǒng)可以在有大共模電壓和噪聲的情況下測(cè)量大信號(hào)(±20 V或以上)��,堪稱高性能����、低壓ADC的理想前端。

推薦閱讀: