【導(dǎo)讀】在優(yōu)化數(shù)據(jù)采集(DAQ)系統(tǒng)時�,設(shè)計人員必須仔細(xì)考慮電源對高精度性能的影響。電源電路中通常都包含低壓差線性穩(wěn)壓器和DC-DC開關(guān)模式轉(zhuǎn)換器的組合�����。開關(guān)模式轉(zhuǎn)換器的一個缺點是:它們會產(chǎn)生輸出紋波�����。雖然紋波幅度相對較低����,但它們會耦合到模擬信號路徑的關(guān)鍵元件中,可能會破壞測量和降低性能��。電源元件通常必須具備極低的噪聲�����,并且在PCB的多個位置進(jìn)行充分的電源去耦��,以防止信號鏈的性能下降�。

電源電壓抑制比(PSRR)是衡量系統(tǒng)抑制電源噪聲和干擾能力的量化指標(biāo)。隨著DAQ解決方案通過系統(tǒng)級封裝(SiP)技術(shù)發(fā)展成為更完整的信號鏈解決方案��,可將電源去耦和精密信號鏈封裝在一起��,以提高整個系統(tǒng)的PSRR����。

PSRR定義

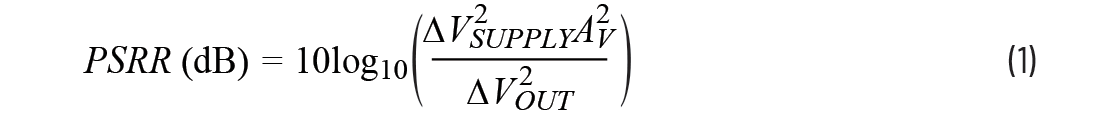

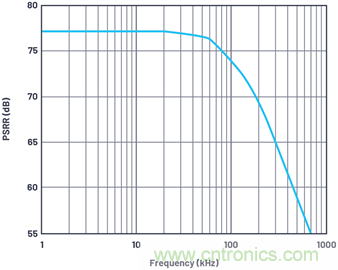

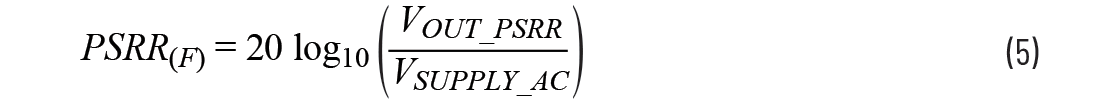

電源電壓抑制比也稱為電源紋波抑制,實質(zhì)上是電源電壓變化與輸出電壓的比值��,用dB表示����。

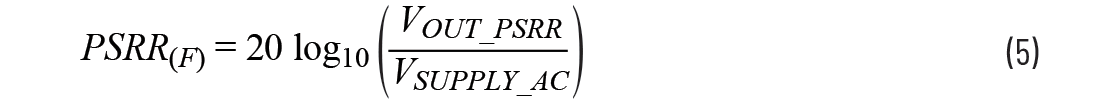

以下公式定義了如何計算PSRR (A2V為電壓增益)。

PSRR是一個重要的參數(shù)�,用于量化電路對電源噪聲和擾動的敏感度及其對電路輸出的影響����。通常在較寬的頻率范圍(直流到數(shù)MHz)內(nèi)測量����,PSRR會隨頻率升高而降低。

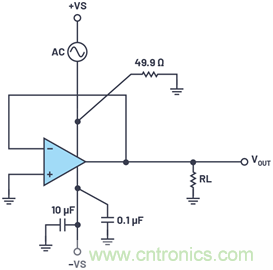

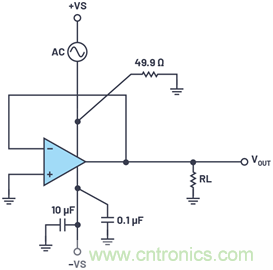

系統(tǒng)設(shè)計人員經(jīng)常在電路的電源節(jié)點中添加解耦電容���,以減少可能耦合到敏感元件中的噪音和毛刺。對于放大器����,將0.1 µF陶瓷電容放置在盡量靠近電源引腳的位置,以減少高頻耦合����。此外,為了提供低頻解耦�����,可并聯(lián)連接較大的10 μF鉭電容�,一般將其放置在更靠近電源的位置。

PSRR推動因素

一些系統(tǒng)設(shè)計人員不愿使用高功耗���、低噪聲功率轉(zhuǎn)換元件��,其中一個原因是他們希望獲得高功效比��。電池供電的DAQ系統(tǒng)就是這種要求以低功耗獲取高性能的應(yīng)用�,因此需要設(shè)計對電源噪聲不敏感的DAQ系統(tǒng)。

現(xiàn)代設(shè)備通常包含多個由同一電池供電的系統(tǒng)����。在一定條件下,如果一個系統(tǒng)或設(shè)備的功耗增加����,那么電池電壓,以及由該電池供電的其他設(shè)備的電源電壓都可能發(fā)生變化���。由于這些原因���,在設(shè)計系統(tǒng)的電池管理電路時,dc PSRR參數(shù)非常重要�����。設(shè)計人員可以根據(jù)系統(tǒng)的靈敏度����,使用LDO穩(wěn)壓器來幫助消除壓降�。在電池供電系統(tǒng)中�����,如果需要紋波觸發(fā)降壓�、升壓或反相穩(wěn)壓器,則AC PSRR也是一個重要參數(shù)�。

對于工業(yè)應(yīng)用,系統(tǒng)噪聲是關(guān)鍵指標(biāo)�����。例如��,附近設(shè)備的電磁干擾(EMI)會與電源耦合�,導(dǎo)致出現(xiàn)噪聲雜散和其他誤差����。為了幫助最大限度減少這些噪聲雜散,使用解耦電容和合適的PCB設(shè)計技術(shù)(例如接地�����、屏蔽,以及正確放置元件)非常重要��。

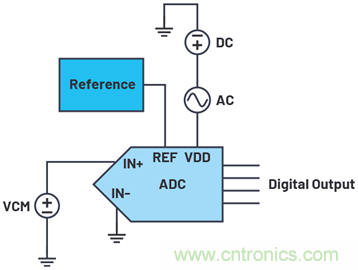

圖1展示典型的精密數(shù)據(jù)采集系統(tǒng)信號鏈�。各個元件都不同程度地受電源噪聲的影響。添加合適的解耦電容���,可以提高圖1所示的信號鏈各元件在更高頻率下的PSRR性能�����。

圖1.典型的精密數(shù)據(jù)采集信號鏈��。

ADI公司的信號鏈µModule®數(shù)據(jù)采集解決方案可以幫助解決一些電源設(shè)計難題����,例如優(yōu)化線路布局���、添加解耦電容�,以及在某些情況下�,添加電源管理元件,例如LDO穩(wěn)壓器����。ADAQ4003是一款µModule數(shù)據(jù)采集解決方案��,所有電源都包含解耦電容��,以降低其對擾動的敏感度�����。 ADAQ7980/ADAQ7988µModule數(shù)據(jù)采集系統(tǒng)包括解耦電容和一個LDO穩(wěn)壓器�����。 集成式LDO穩(wěn)壓器可以進(jìn)一步簡化設(shè)計——系統(tǒng)設(shè)計人員只需提供一個干凈電源為µModule器件供電��,如果需要�,還可以旁路LDO穩(wěn)壓器����。

當(dāng)前測試分立元件PSRR的方法

分立元件PSRR測試是特性表征計劃中的常見組成部分�����,它采用一套完善的標(biāo)準(zhǔn)和方法進(jìn)行����。分立元件PSRR測試通常在沒有任何外部電源去耦電容的情況下進(jìn)行�,以揭示供電軌上的大量噪聲對性能的直接影響���。

通常�,可以使用函數(shù)發(fā)生器和示波器����,或者使用網(wǎng)絡(luò)分析儀,通過向直流電源電壓注入不同的頻率����,并測量DUT輸出的擾動量來確定放大器的PSRR特性。

圖2.分立式PSRR測試電路示例�����。

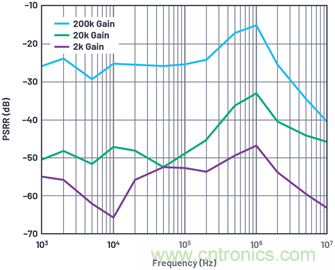

對分立器件執(zhí)行ac PSRR測試需要將交流信號注入直流電源電壓����,并測量相對于電源激勵的輸出干擾。例如����,在100 kHz頻率下,ADA4945的PSRR為115 dB。這意味著電源上1 VPEAK, 100 kHz的交流干擾表現(xiàn)為器件輸出端約1.79 µVPEAK的電壓信號��。

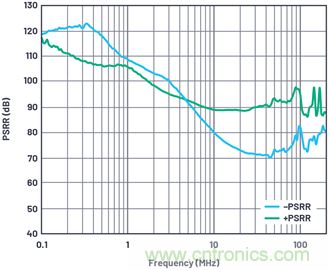

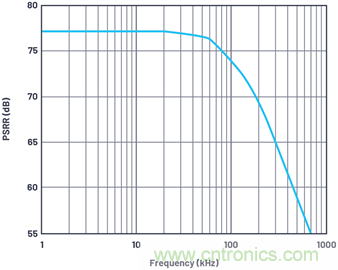

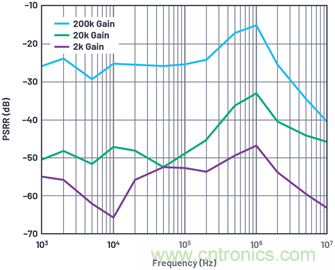

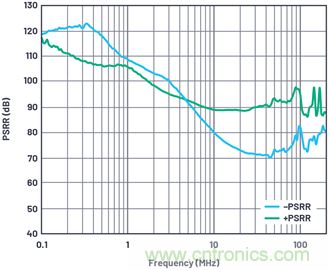

圖3.ADA4945全差分ADC驅(qū)動器的PSRR與頻率的關(guān)系����。

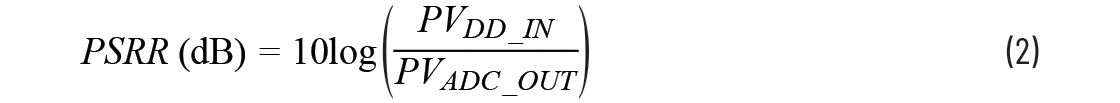

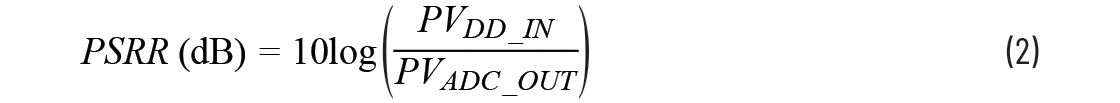

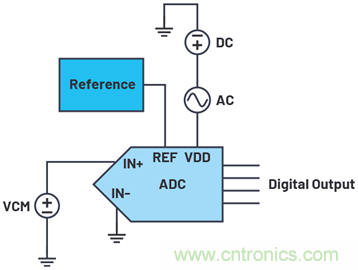

測試ADC的PSRR性能與測試放大器類似,但它不是測試電壓輸出���,而是數(shù)字碼輸出����。對于ac PSRR���,ADC的PSRR是該頻率下ADC輸出功率與該頻率下施加于ADC VDD電源的200 mV p-p正弦波功率的比值�����。圖4和圖5分別顯示SAR ADC的測試配置和得到的典型響應(yīng)�。

對于dc PSRR測試��,誤差是由于電源電壓偏離標(biāo)稱值而引起的滿量程轉(zhuǎn)換點的最大變化�����。

圖4.單端ADC ac PSRR測試電路���。

圖5.ADC ac PSRR響應(yīng)��。

測試SiP以確定PSRR的挑戰(zhàn)在于:它們包含多個高達(dá)30 µF的內(nèi)部旁路電容���,且大部分信號發(fā)生器和網(wǎng)絡(luò)分析儀需要竭力在更高頻率下驅(qū)動如此大的電容負(fù)載。

如何確定信號鏈µModule解決方案的PSRR特性

確定信號鏈µModule解決方案的PSRR特性時�����,使用的測試方法基本上與測試放大器時使用的方法相同���。在直流電源電壓上疊加一個交流信號����,然后測量電源激勵和µModule輸出之間的關(guān)系���。但是����,受內(nèi)部電源解耦電容影響����,在電源的輸入頻率增加時�,也需要信號源提供更高的電流驅(qū)動能力�。內(nèi)部電容確實可以提高對ac PSRR的抗干擾能力,但該測試旨在考慮最糟糕的情況��。

信號鏈µModule解決方案可用于各種應(yīng)用����,所以在最終應(yīng)用中,必須和測試分立元件一樣測試SiP的PSRR����。雖然包含多個分立元件,但很難預(yù)測整個系統(tǒng)會如何響應(yīng)交流電源激勵����。

從特性表征角度來看,要正確測試PSRR��,首要考慮因素包括內(nèi)部旁路電容和合適的評估板設(shè)計(本文的“評估板開發(fā)設(shè)計考量”一節(jié)會進(jìn)一步介紹評估板設(shè)計)���。任何內(nèi)部旁路電容都會提高信號鏈µModule解決方案的ac PSRR����,但這種電容也會影響執(zhí)行測試的方式。

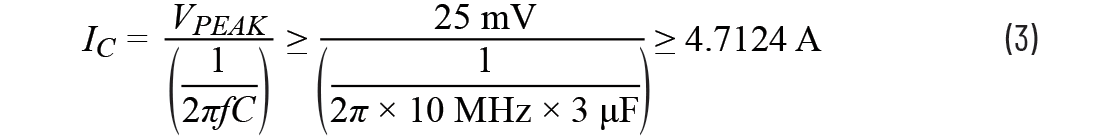

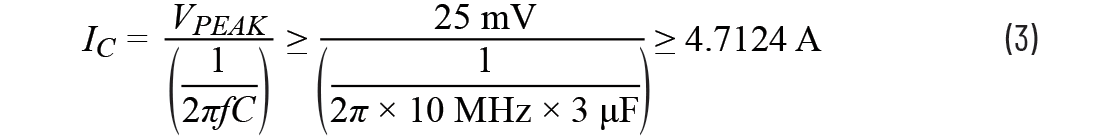

如前所述���,信號發(fā)生器不具備驅(qū)動較大電容負(fù)載的能力。例如���,如果信號鏈µModule解決方案的主電源上總共有3 µF內(nèi)部旁路電容�����,并且PSRR測試需要最高10 MHz頻率和50 mV p-p振幅�。根據(jù)這些條件�����,生成正弦波的信號發(fā)生器需要能夠驅(qū)動約4.71 A電流����,并且具有足夠帶寬來處理10 MHz信號。這是基于解耦電容在10 MHz時的電阻得出��。

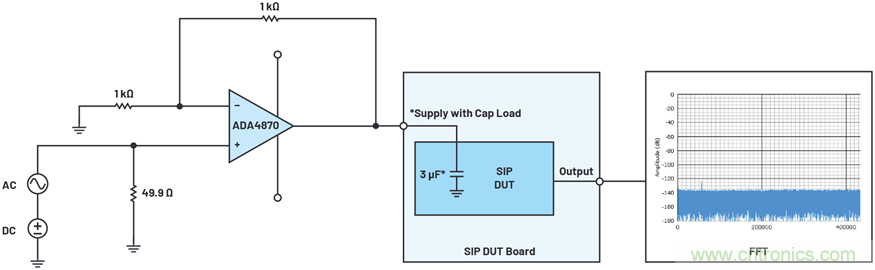

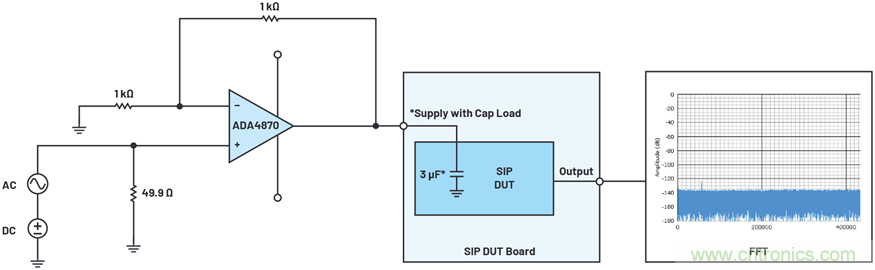

要提供足夠電流����,可以使用高功率放大器(例如ADA4870)來提供額外的源電流能力����。此設(shè)置假設(shè)使用的函數(shù)發(fā)生器可以提供偏置DUT所需的直流電壓���。如果不是這種情況�,可以使用偏置器來隔離直流和交流信號路徑�,或者可以從給定的信號發(fā)生器獲取可用的直流偏置,以滿足其他所需的輸出要求�。

圖6.使用ADA4870的PSRR設(shè)置框圖。

ADA4870評估板具備SMA輸入和SMA輸出��,因此能夠提供一種相對簡單的方法來連接評估板和信號發(fā)生器��。

評估板開發(fā)設(shè)計考量

設(shè)計也可用于實施PSRR測試的評估板并不等于要大幅變更設(shè)計����。牢記以下幾點:

● 對于要實施PSRR測試的每個電源,需提供一個通過SMA驅(qū)動的選項�,以保持信號源信號的完整性。

● 注意減少從SMA輸入到DUT上相關(guān)電源層這一路徑中的任何寄生電感和電容�����。任何寄生電容或電感都可能在相關(guān)頻率產(chǎn)生干擾諧振�����。

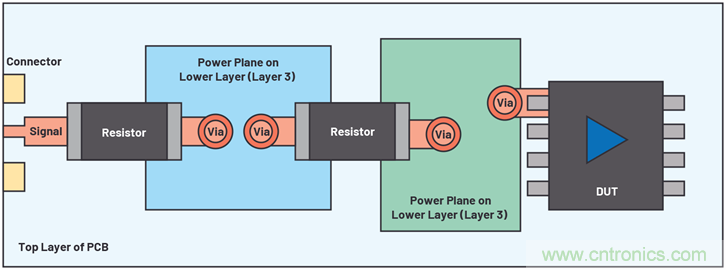

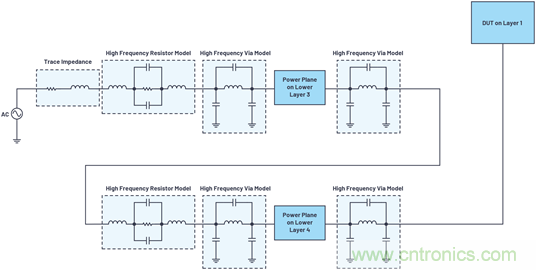

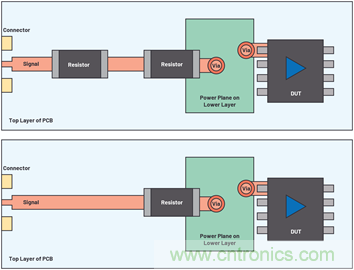

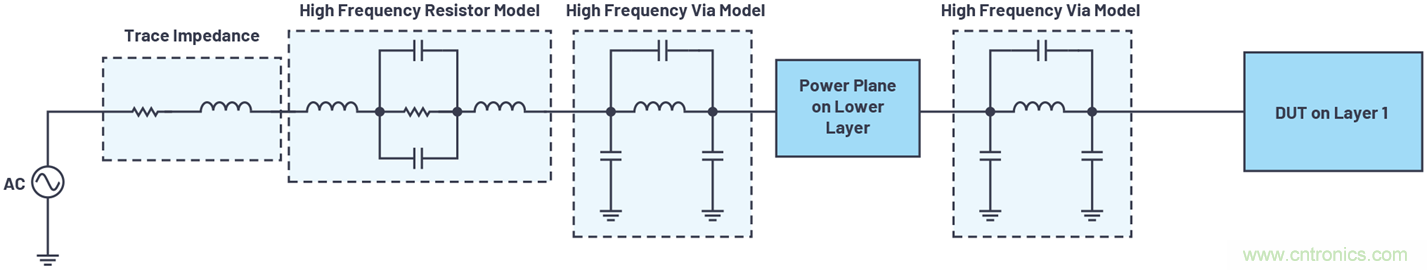

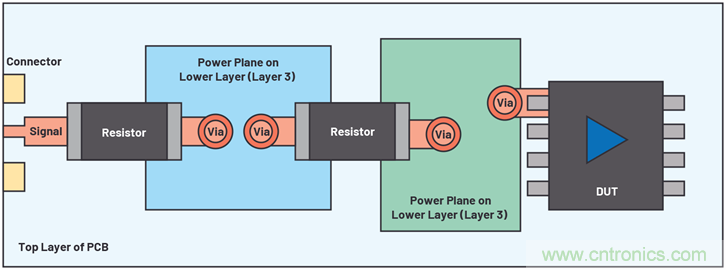

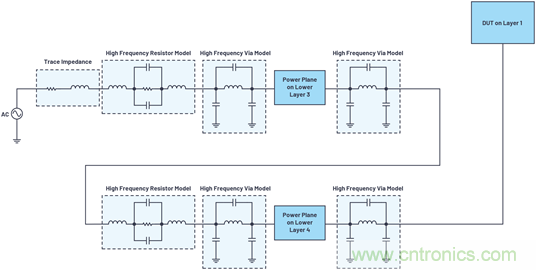

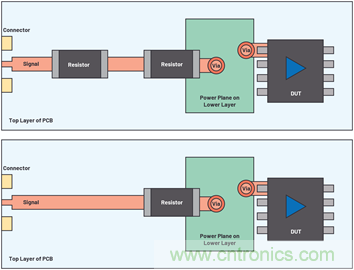

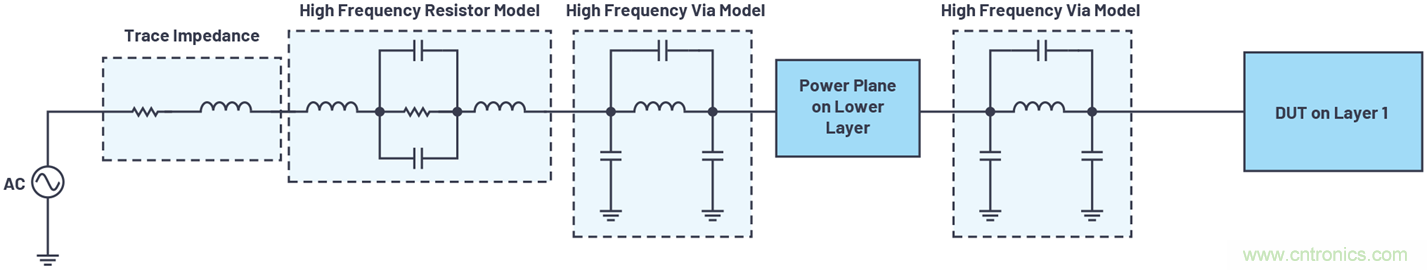

● 對于每個電源,確保其相關(guān)電源層是整體�����,也就是說����,不會被無源元件和多個層分成多個部分����。例如,一個電流檢測電阻不應(yīng)橫跨兩個電源層(如圖7所示)�。此外,盡量減少電源跨層的次數(shù)�����,避免通孔產(chǎn)生寄生電感���,如圖8中的高頻模型所示�����。圖7所示的電阻可用于電流檢測���,但在這種情況下����,它們?yōu)? Ω�����。圖9顯示更好的PCB電源層布線��,圖10則顯示高頻等效模型��。

圖7.不良的電源層連接設(shè)計示例��。/figcaption>

圖8.圖7的高頻等效原理圖��。

圖9.優(yōu)化PCB電源層布線:更優(yōu)性能�。

圖10.圖9的高頻等效原理圖。

必須在沒有DUT的情況下測試評估板���,以確保相關(guān)頻率范圍內(nèi)沒有任何干擾諧振�����。如果存在諧振����,應(yīng)在數(shù)據(jù)處理期間加以解決。對于每個頻率�����,都要通過示波器驗證電源信號是否符合預(yù)期����,不要相信信號發(fā)生器上的撥盤�����。

測試設(shè)置

如前所述���,受測信號鏈µModule解決方案的電源必須能夠提供額定直流偏置���,以便在最大輸入頻率下為DUT供電,為交流激勵提供足夠電流�����。要在圖中所示的設(shè)置中實現(xiàn)這一目標(biāo),需結(jié)合使用ADA4870評估板(同相增益為2)和AD3256函數(shù)發(fā)生器���。

圖11顯示自定義的ADA4870功率放大器評估板和ADA4355評估板���。

圖11.用于執(zhí)行PSRR測試的ADA4355評估板和ADA4870評估板。

圖12中所示的數(shù)據(jù)是通過捕捉每個輸入頻率下的數(shù)據(jù)并查看每個頻率下FFT (dBFS)的功率而生成的�����?�?梢允褂霉?求解該頻率下的電壓電平:

利用得出的 VOUT_PSRR來計算PSRR:

圖12.ADA4355 PSRR測試結(jié)果��。

結(jié)論

ADI公司的信號鏈µModule解決方案集成了信號調(diào)理����、電源產(chǎn)生和無源內(nèi)部元件。這些一體化系統(tǒng)級封裝設(shè)計有助于客戶在極小的PCB尺寸空間內(nèi)快速實現(xiàn)符合市場需求的預(yù)期性能�����。雖然信號鏈µModule解決方案簡單易用��,但必須進(jìn)行適當(dāng)?shù)臏y試。盡管可以采用PSRR標(biāo)準(zhǔn)測試方法���,但由于標(biāo)準(zhǔn)設(shè)備本身的限制��,通常需要額外的電流驅(qū)動能力����。

參考電路

“運算放大器電源電壓抑制比(PSRR)與電源電壓����。”(ADI公司,2009年)

Reeder, Rob�。“高速ADC的電源設(shè)計,” ADI公司��,2012年2月����。

Morita, Glenn����。 “理解低壓差穩(wěn)壓器(LDO)概念,實現(xiàn)系統(tǒng)優(yōu)化設(shè)計���。” 模擬對話,第48卷第12期�����,2014年12月����。

Walsh, Alan。“在功率敏感型應(yīng)用中利用高效率�、超低功耗開關(guān)穩(wěn)壓器為精密SAR ADC供電。” ADI公司�,2016年3月。

推薦閱讀: