【導(dǎo)讀】時(shí)鐘設(shè)備設(shè)計(jì)使用I2C可編程小數(shù)鎖相環(huán)(PLL),可滿足高性能時(shí)序需求,這樣可以產(chǎn)生零PPM(百萬分之一)合成誤差的頻率。高性能時(shí)鐘IC具有多個(gè)時(shí)鐘輸出,用于驅(qū)動(dòng)打印機(jī)、掃描儀和路由器等應(yīng)用系統(tǒng)的子系統(tǒng)。此類復(fù)雜系統(tǒng)需要?jiǎng)討B(tài)更新參考時(shí)鐘的頻率,以實(shí)現(xiàn) PCIe和以太網(wǎng)等其它諸多協(xié)議。

時(shí)鐘 IC 屬于 I2C 從器件,需要主控制器來配置內(nèi)部 PLL 邏輯,其控制邏輯可以寫入微控制器內(nèi)。作為 I2C 主機(jī),微控制器將配置寫入時(shí)鐘 IC 的內(nèi)部易失性存儲(chǔ)器并控制 PLL。因此,可以通過板上 MCU - IC 組合進(jìn)行系統(tǒng)時(shí)鐘頻率的動(dòng)態(tài)更新。可編程微控制器為高性能時(shí)鐘 IC 提供控制邏輯能力,通過減少板載 IC和板上走線使整體設(shè)計(jì)更加緊湊,并降低最終物料成本。

操作理論

圖 1 為高性能時(shí)鐘設(shè)備的基本 PLL 架構(gòu)。該設(shè)計(jì)使用比例因子為 PLL 輸出端口提供時(shí)鐘合成。最終輸出頻率的基本公式為:

· fREF 為輸入?yún)⒖季w頻率(在多數(shù)應(yīng)用中通常為 8 MHz 至 48 MHz)。

· DIV_R(DIV_R1 和 DIV_R2)是輸入頻率參考的分頻因子。此類分頻器名為預(yù)分頻器。

· DIV_N 為小數(shù) N 分頻因子。

· DIV_O(DIV-O1、DIV-O2、DIV-O3 和 DIV-O4)為輸出前的后分頻因子。

圖1.簡化高性能時(shí)鐘的 PLL 架構(gòu)框圖

圖1中的橙色框圖為參數(shù),使用這些參數(shù)的方程式為可編程方程式。這些參數(shù)可以在出廠時(shí)寫入時(shí)鐘設(shè)備的非易失性存儲(chǔ)器。時(shí)鐘設(shè)備具有內(nèi)部易失性和非易失性存儲(chǔ)器,兩個(gè)存儲(chǔ)器互相復(fù)制其內(nèi)容。非易失性存儲(chǔ)器在出廠時(shí)已被寫入所需配置,在最終應(yīng)用中,當(dāng)設(shè)備啟動(dòng)電源時(shí),非易失性存儲(chǔ)器的內(nèi)容會(huì)被復(fù)制到易失性存儲(chǔ)器。同時(shí),PLL 產(chǎn)生所需的默認(rèn)時(shí)鐘輸出。

時(shí)鐘 IC 的重要特性之一就是通過 I2C 接口實(shí)現(xiàn)運(yùn)行時(shí)可編程。通過可編程功能,用戶可以更改設(shè)備的易失性存儲(chǔ)器內(nèi)容以進(jìn)行即時(shí)更改。只需使用適當(dāng)?shù)?I2C 指令,就可以通過主控制器實(shí)現(xiàn)用戶配置文件的即時(shí)編程功能。

設(shè)備的非易失性存儲(chǔ)器還可以存儲(chǔ)預(yù)定義的多用戶配置。用戶可以使用頻率選擇 (Frequency Select, FS) 功能以選擇其中一個(gè)配置。該 FS - 位為設(shè)備中可用的 CMOS 輸入引腳。FS 引腳應(yīng)用 N - 位外部 CMOS 信號(hào),然后內(nèi)部選擇存儲(chǔ)在非易失性存儲(chǔ)器中的一個(gè)配置文件,這個(gè)配置文件同樣也被復(fù)制到了易失性存儲(chǔ)器,PLL 則輸出不同的信號(hào)。

同時(shí),微控制器通過 I2C 提供數(shù)據(jù)來控制高頻時(shí)鐘。使用微控制器的優(yōu)點(diǎn)是,它具有不同的通信外設(shè)和通信協(xié)議,如 I2C、SPI、UART、藍(lán)牙、ZigBee 等,使得系統(tǒng)能夠以主從配置將數(shù)據(jù)傳輸?shù)狡渌⒖刂破?,也可以使用一個(gè)自定義的應(yīng)用傳輸至安卓和 iOS 設(shè)備。此外,微控制器還配有各種 IDE 工具用于簡化設(shè)計(jì)。這可以更好地證明使用 I2C 指令來配置 PLL 參數(shù)、編寫并驗(yàn)證定制應(yīng)用程序是合適的。

高性能時(shí)鐘的應(yīng)用需求

高性能時(shí)鐘 IC 專為消費(fèi)者、工業(yè)和網(wǎng)絡(luò)應(yīng)用而設(shè)計(jì)。此類時(shí)鐘 IC 具有多個(gè)從不同 PLL 導(dǎo)出的差分輸出和單端輸出,并且可以通過 I2C 接口實(shí)現(xiàn)可編程功能。此外,高性能時(shí)鐘 IC不僅可以支持 PCI Express (PCIe) 1.0 / 2.0 / 3.0、USB 2.0 / 3.0 和萬兆以太網(wǎng) (GbE)等關(guān)鍵接口標(biāo)準(zhǔn)的參考時(shí)鐘。還能支持壓控晶體振蕩器 (VCXO) 和頻率選擇 (FS)等其他增值功能。

高性能時(shí)鐘 IC 采用設(shè)計(jì)實(shí)現(xiàn) I2C 從機(jī)模式。因此,需要一個(gè)板載 I2C 主機(jī)來控制以下可編程功能:

· 通過 I2C 接口進(jìn)行系統(tǒng)內(nèi)編程

· 通過頻率選擇 (FS) 引腳更新配置

· 外部復(fù)位操作

· 壓控晶體振蕩器 (VCXO) 操作

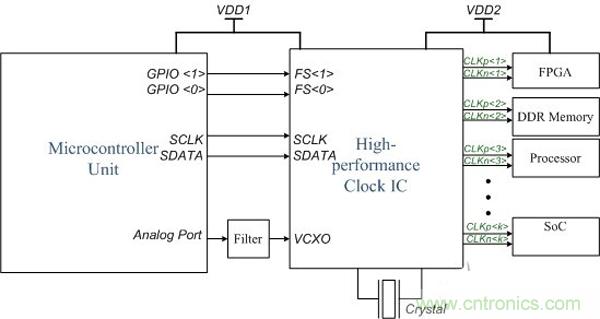

圖2.微控制器 - 高性能時(shí)鐘接口電路

微控制器在時(shí)鐘 IC PLL 控制中的作用

如圖 2 所示,將時(shí)鐘 IC 連接到微控制器電路。時(shí)鐘 IC 具有內(nèi)部 PLL 模塊,其功能是提供作為固定直流電壓的調(diào)諧電壓 (Vtune) ,而調(diào)諧電壓將隨頻段而變化。PLL 模塊在輸入端接收本地振蕩器頻率,由內(nèi)部前置放大器放大信號(hào)。另外,預(yù)分頻器對(duì)輸入頻率進(jìn)行下變頻,并將其作為輸入傳送至相位比較器。

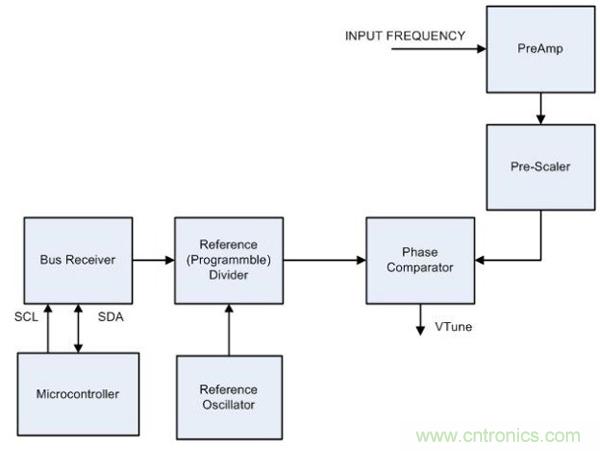

圖3.PLL 模塊的微控制器控制

微控制器通過 I2C 發(fā)送數(shù)據(jù)到可編程分頻器。該分頻器也接收來自參考振蕩器(例如 4 MHz 晶體振蕩器)的輸入。相位比較器(即相位檢測(cè)器)通過預(yù)分頻器接收本地振蕩器頻率(例如 87.15 MHz),還通過參考分頻器和參考振蕩器接收微控制器的輸入(例如,87.15 MHz)。如果兩個(gè)輸入都匹配,相位比較器將提供 Vtune 調(diào)諧電壓。一旦本地振蕩器頻率與微控制器頻率數(shù)據(jù)之間稍有不匹配,都將無法提供調(diào)諧電壓 (Vtune) 和輸出。圖 3 所示為完整的框圖。

在微控制器的幫助下,PLL 通過調(diào)諧本地振蕩器頻率產(chǎn)生閉環(huán),并在輸出端產(chǎn)生調(diào)諧電壓。調(diào)諧電壓將從較低頻率信道增加到較高頻率信道。通過改變預(yù)分頻器和可編程分頻器的值,微控制器可以調(diào)整步長。

步長 =(本地振蕩器頻率/預(yù)分頻器)X(可編程分頻器/參考振蕩器)

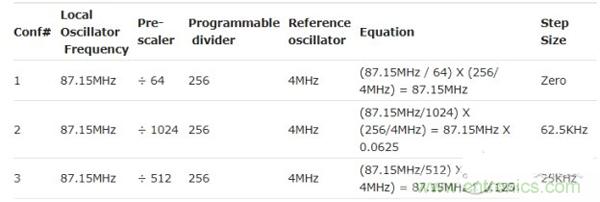

表1所示為部分配置

通過 I2C 接口進(jìn)行系統(tǒng)內(nèi)編程

系統(tǒng)內(nèi)編程可為系統(tǒng)設(shè)計(jì)實(shí)現(xiàn)快速有效的迭代。編程數(shù)據(jù)序列可通過 SCL 和 SDA 引腳傳送到時(shí)鐘器件,把操作順序編程至板載微控制器(主設(shè)備)中,通過命令和數(shù)據(jù)在運(yùn)行時(shí)與從機(jī)時(shí)鐘進(jìn)行交互。

此處為系統(tǒng)示例,其中時(shí)鐘信號(hào)必須以采樣率的倍數(shù)為準(zhǔn)。該時(shí)鐘頻率在 155.52 MHz 和 156.25 MHz 兩組頻率之間變動(dòng)。這意味著驅(qū)動(dòng)串行控制器的時(shí)鐘必須能夠在這兩個(gè)值之間靈活切換。微控制器主設(shè)備可以訪問并修改寫入易失性存儲(chǔ)器的 PLL 配置,從而滿足這兩個(gè)頻率需求。

通過頻率選擇 (FS) 引腳更新配置

高性能時(shí)鐘設(shè)備支持包含個(gè)性化配置的多個(gè)用戶配置文件。在 FS 引腳轉(zhuǎn)換方面,高性能時(shí)鐘器件具有兩個(gè)時(shí)序規(guī)格 - 快速切換和慢速切換。

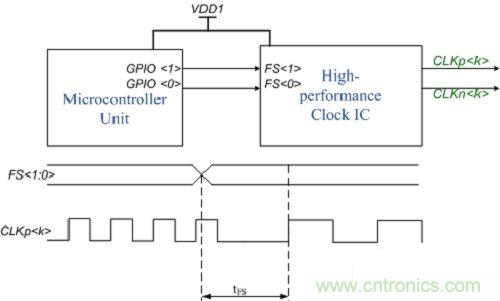

快速切換適用于輸出 ON/OFF 、輸出分頻值變化,以及輸出 MUX 設(shè)置更改。慢速切換則適用于更改 PLL 參數(shù)(包括 PLL ON/OFF)。顧名思義,快速切換中的輸出變化更快,而慢速切換的速度較慢。兩種切換類型都可以打開或關(guān)閉輸出,并且不出絲毫差錯(cuò)。圖 4 所示為 FS 與輸出時(shí)鐘之間的時(shí)序關(guān)系。

圖4.頻率選擇操作

外部復(fù)位操作:

當(dāng)外部復(fù)位生效時(shí),時(shí)鐘 IC 進(jìn)入低功耗模式。輸出和 I2C 總線信號(hào)處于高阻抗 (HI-Z) 狀態(tài),直到取消外部復(fù)位并完成初始化。外部復(fù)位重啟易失性存儲(chǔ)器內(nèi)容,存儲(chǔ)在非易失性存儲(chǔ)器中的配置則被復(fù)制到易失性存儲(chǔ)器。當(dāng)需要重新初始化任意一個(gè)系統(tǒng)中運(yùn)行的應(yīng)用程序時(shí),該功能將被使用。

壓控晶體振蕩器 (VCXO) 操作:

對(duì)某些應(yīng)用而言,輸出時(shí)鐘頻率應(yīng)通過使用模擬反饋跟蹤輸入數(shù)據(jù)流。如圖 5 所示,時(shí)鐘 IC 作為大鎖相環(huán)的一部分。ASIC 或 SoC 負(fù)責(zé)跟蹤輸入流、計(jì)算誤差并產(chǎn)生 PWM 信號(hào)(通常來說),隨后將誤差信息反饋至本地時(shí)鐘發(fā)生器以進(jìn)行頻率調(diào)諧。

圖5.VCXO 示例電路

VCXO 功能能夠修改 PLL 頻率,因此頻率牽引不依賴于晶體特性、溫度、電壓或設(shè)備工藝。VCXO 調(diào)制是線性、精準(zhǔn)調(diào)制。也可以使用時(shí)鐘參考。通過微控制器的內(nèi)置模擬模塊,VCXO 的控制邏輯精準(zhǔn)到小數(shù)點(diǎn)后 6 位。

作為 I2C 主設(shè)備,微控制器將配置寫入時(shí)鐘 IC 的內(nèi)部易失性存儲(chǔ)器并控制 PLL。因此,通過板載 MCU-IC 組合可以實(shí)現(xiàn)系統(tǒng)時(shí)鐘頻率的動(dòng)態(tài)更新。開發(fā)人員可以使用可編程微控制器,為高性能時(shí)鐘 IC 提供控制邏輯。這可以減少對(duì)板載 IC 和走線數(shù)量的需求,使得整個(gè)系統(tǒng)設(shè)計(jì)更加緊湊。

微控制器配備強(qiáng)大 IDE 工具,可以加速應(yīng)用開發(fā)。集成可編程片上系統(tǒng)(PSoC)器件可進(jìn)一步簡化設(shè)計(jì)并有助于降低整體產(chǎn)品成本。