【導(dǎo)讀】一個(gè)良好設(shè)計(jì)差分對(duì)是成功進(jìn)行高速數(shù)據(jù)傳輸?shù)年P(guān)鍵因素。根據(jù)應(yīng)用的不同,差分對(duì)可以是一對(duì)印刷電路板 (PCB) 走線,一對(duì)雙絞線或一對(duì)共用絕緣和屏蔽的并行線。在這一系列中,我將討論差分對(duì)的特點(diǎn),以及針對(duì)高速數(shù)據(jù)傳輸?shù)脑O(shè)計(jì)問題和解決方案。

對(duì)于速度的渴求始終在增長,傳輸速率每隔幾年就會(huì)加倍。這一趨勢在諸如計(jì)算、SAS和SATA存儲(chǔ)方面的PCIe以及云計(jì)算中的千兆以太網(wǎng)等很多現(xiàn)代通信系統(tǒng)中很普遍。信息革命對(duì)通過傳輸介質(zhì)傳送數(shù)據(jù)提出了巨大挑戰(zhàn)。目前的傳輸介質(zhì)仍然依賴于銅線,數(shù)據(jù)鏈路中的信號(hào)速率可以達(dá)到大于25Gbps,并且端口吞吐量可以大于100Gbps。

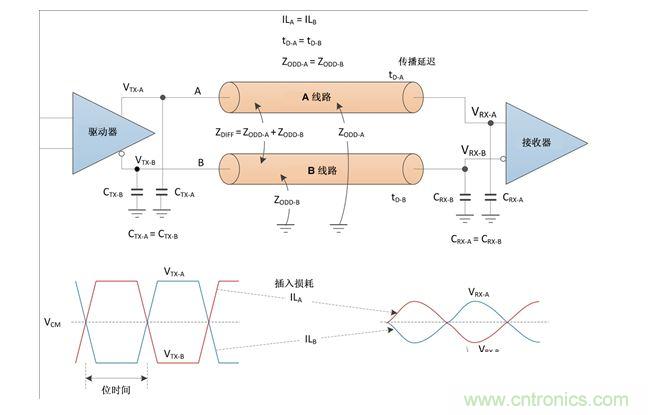

這些串行數(shù)據(jù)傳輸設(shè)計(jì)使用差分信號(hào)的方式,通過被稱為差分對(duì)的一對(duì)銅線來傳送數(shù)據(jù)。A線路和B線路內(nèi)的信號(hào)是等振幅、反相位高速脈沖。差分信號(hào)在很多電路上有使用,比如LVDS,CML和PECL等等。

傳送一個(gè)理想的串行比特流

串行比特流是通過一個(gè)差分對(duì)傳播的差分信號(hào)。如圖1所示,差分信號(hào)的預(yù)計(jì)到達(dá)時(shí)間是一樣的,這樣的話,它們在接收端上保持差分信號(hào)的屬性(等振幅、反相位)。一個(gè)接收器被用來恢復(fù)信號(hào),然后正確地采樣和恢復(fù)數(shù)據(jù),從而實(shí)現(xiàn)無誤差數(shù)據(jù)傳輸。

圖1:理想差分對(duì)的電氣屬性

對(duì)于差分對(duì)的要求

一個(gè)良好設(shè)計(jì)差分對(duì)是成功進(jìn)行高速數(shù)據(jù)傳輸?shù)年P(guān)鍵因素。根據(jù)應(yīng)用的不同,差分對(duì)可以是一對(duì)印刷電路板 (PCB) 走線,一對(duì)雙絞線或一對(duì)共用絕緣和屏蔽的并行線(通常稱為Twin-axial電纜)。在這一系列中,我將討論差分對(duì)的特點(diǎn),以及針對(duì)高速數(shù)據(jù)傳輸?shù)脑O(shè)計(jì)問題和解決方案。

在這一系列的第一部分中,讓我們研究一下差分對(duì)的主要要求:

A線路和B線路都需要保持相當(dāng)恒定和相等的特性阻抗,通常稱為奇模阻抗,此時(shí)兩條線路均差分激勵(lì)。

差分信號(hào)應(yīng)該在到達(dá)目的端時(shí)保持差分信號(hào)的屬性:幾乎相等的振幅和相反的相位。

每條線路的插入損耗應(yīng)該大致相等。

每條線路的傳播延遲應(yīng)該大致相等。

總之,我們應(yīng)該尋求相等并且相當(dāng)恒定的奇模阻抗,從而最大限度地減少從源端到目的端整條差分對(duì)長度上的阻抗波動(dòng)。我們也應(yīng)當(dāng)使A線路與B線路之間的延遲匹配和插入損耗匹配。此外,我們需要確保插入損耗不會(huì)太多,這樣的話,接收器能夠正確地恢復(fù)數(shù)據(jù)。

為了滿足上述要求,A線路和B線路應(yīng)該在它們的物理布局布線中保持高對(duì)稱。發(fā)射器和接收器也應(yīng)該在它們的A和B線路電路中保持高對(duì)稱,這樣的話,它們在A線路和B線路上的電氣負(fù)載相等。

設(shè)計(jì)差分對(duì),以最大限度地減少失真

在理想情況下,差分對(duì)是完全對(duì)稱的,此時(shí)具有無限帶寬并且鄰近信號(hào)之間完全隔離。在現(xiàn)實(shí)情況下,差分信號(hào)通過集成電路 (IC) 封裝、外部器件、不同的PCB結(jié)構(gòu)、連接器和電纜連接子系統(tǒng)進(jìn)行傳播。實(shí)現(xiàn)完全對(duì)稱的差分對(duì)是件不太容易的事情。在以后的博文中,我將討論差分對(duì)設(shè)計(jì)的方案,以及最大限度減少發(fā)射信號(hào)失真的技術(shù)。

德州儀器 (TI) 擁有完整的高速信號(hào)調(diào)理IC產(chǎn)品線,諸如重定時(shí)器(Retimer)和驅(qū)動(dòng)器(Redriver)。它們在解決所有類型實(shí)際差分對(duì)設(shè)計(jì)時(shí)碰到的不理想情況,和高插入損耗情況大有幫助,從而在現(xiàn)代系統(tǒng)中實(shí)現(xiàn)了可靠數(shù)據(jù)通信并延長了傳輸距離。