【導(dǎo)讀】ADC在實(shí)際應(yīng)用中,經(jīng)常會(huì)出現(xiàn)無(wú)法達(dá)到標(biāo)稱精度的情況,而且還會(huì)出現(xiàn)波形嚴(yán)重失真的問(wèn)題,這一現(xiàn)象長(zhǎng)期困擾著我們的硬件工程師,那么,在實(shí)際的ADC應(yīng)用中,為何會(huì)出現(xiàn)這種情況呢?

前言

ADC在實(shí)際應(yīng)用中,經(jīng)常會(huì)出現(xiàn)無(wú)法達(dá)到標(biāo)稱精度的情況,而且還會(huì)出現(xiàn)波形嚴(yán)重失真的問(wèn)題,這一現(xiàn)象長(zhǎng)期困擾著我們的硬件工程師,那么,在實(shí)際的ADC應(yīng)用中,為何會(huì)出現(xiàn)這種情況呢?

筆者在這里通過(guò)一個(gè)實(shí)例和大家一起共同來(lái)探討 ADC在應(yīng)用中可能會(huì)碰到的問(wèn)題。

案例分享

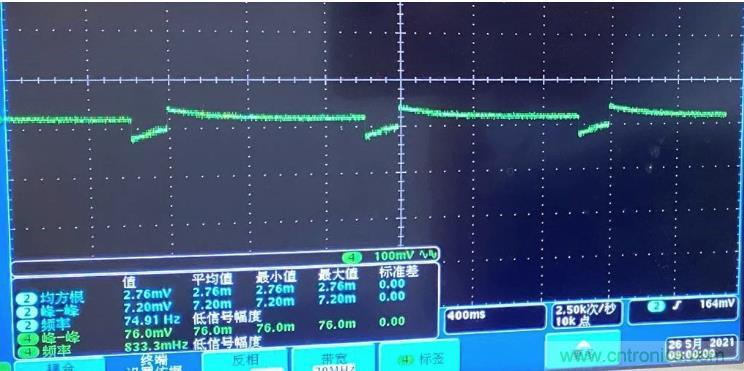

日前,有客戶公司在用某ADC做AD轉(zhuǎn)換的時(shí)候,碰到這樣一個(gè)問(wèn)題,客戶傳感器型號(hào)PT100,在采集信號(hào)時(shí),輸入采樣端的波形如下:

我們首先假定這是一個(gè)直流前端,拋開(kāi)交流耦合等因素,單從這個(gè)采樣波形來(lái)看,采樣端明顯是工作異常的。那么,為何會(huì)出現(xiàn)這種情況呢?

ADC模型初探

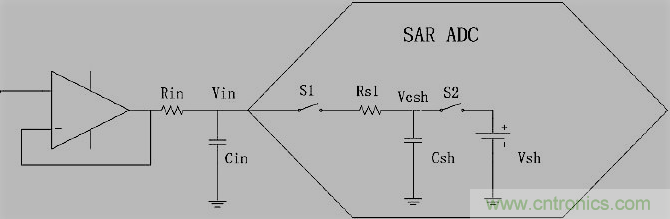

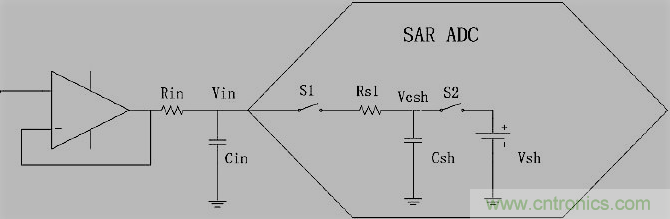

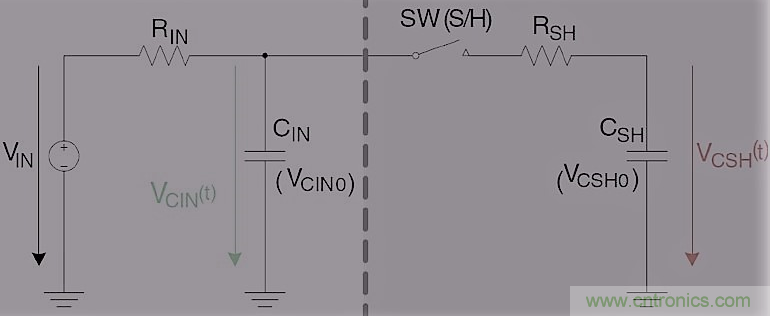

我們先來(lái)大致解剖一下 ADC電路參考模型及其驅(qū)動(dòng)電路,通過(guò)這個(gè)模型來(lái)跟大家共同來(lái)探討一番,為了便于做定量分析,我們?cè)谖闹胁迦胍恍┕?,供大家參考?/div>

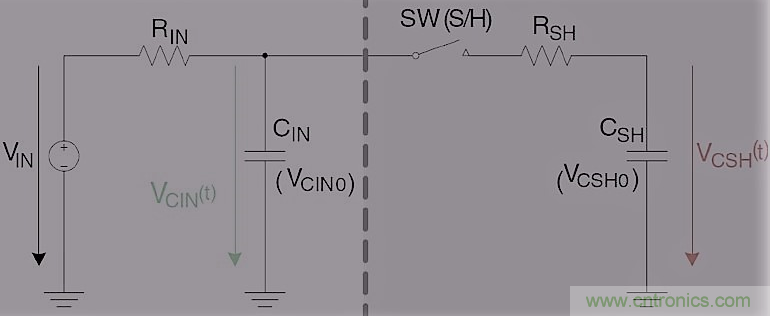

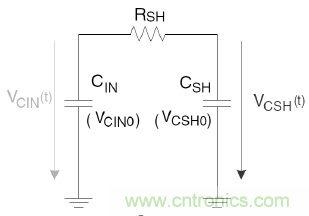

為了更加直觀,我們刪繁就簡(jiǎn),重新整理這個(gè)電路,單看輸入、采樣端的電路模型,大致如下:

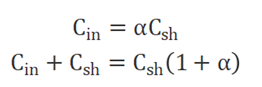

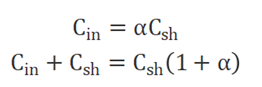

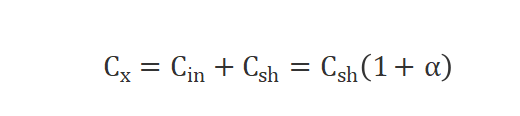

為了簡(jiǎn)化設(shè)計(jì),我們假設(shè)輸入電壓近似于一個(gè)直流電源,拋開(kāi)耦合因素,輸入內(nèi)阻遠(yuǎn)大于采樣電阻,Rin>>Rsh,輸入電容和采樣電容之間的關(guān)系用a來(lái)表示:

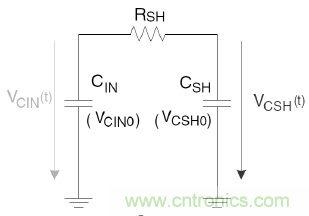

初始狀態(tài),相對(duì)來(lái)說(shuō)Vin向Cin充電相對(duì)較小,主要看Cin向Csh充電過(guò)程,我們構(gòu)建電路模型如下圖所示:

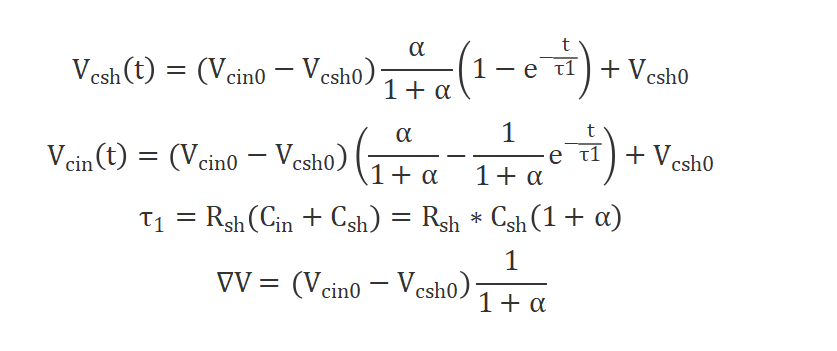

根據(jù)以上模型,可以大致推導(dǎo)出第1階段輸入電壓和采樣電壓對(duì)應(yīng)方程,以及采樣電容充電時(shí)間關(guān)系。

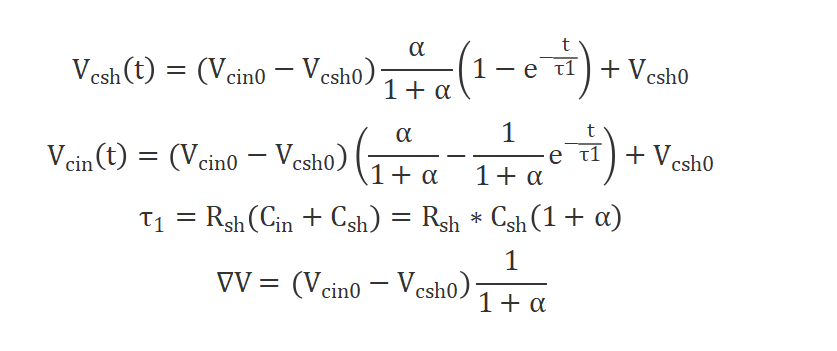

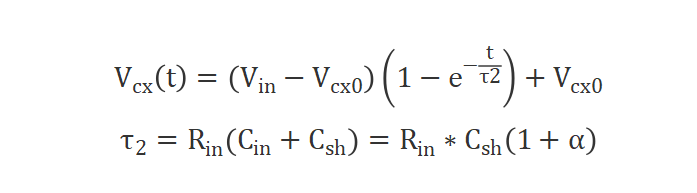

當(dāng)Csh電壓迅速上升到與Cin相當(dāng)之后,我們忽略Rsh對(duì)電路的影響,我們重新構(gòu)建第2階段電路模型如下。

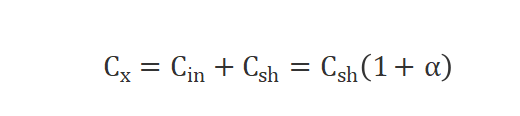

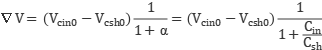

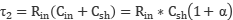

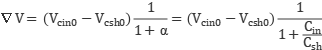

此時(shí),等效電容為輸入電容和采樣電容并聯(lián),根據(jù)以上模型,可以大致推導(dǎo)出輸入電壓和采樣電壓對(duì)應(yīng)方程如下:

此時(shí),根據(jù)等效模型,我們可以推導(dǎo)出正常狀態(tài)下:

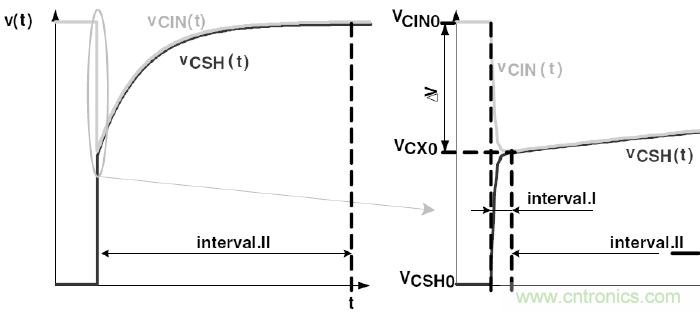

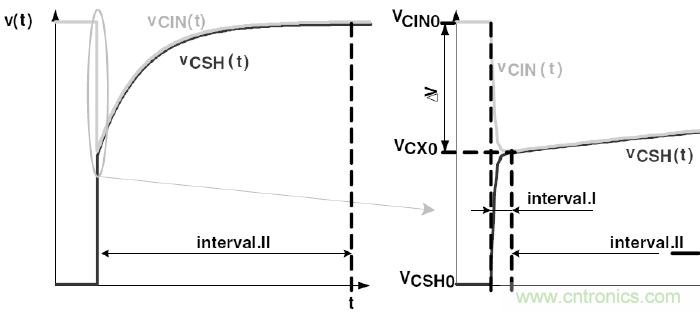

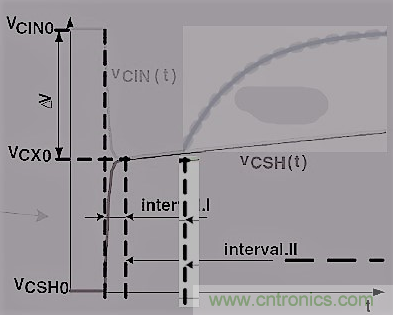

由此,我們可以畫(huà)出采樣端波形大致如下:

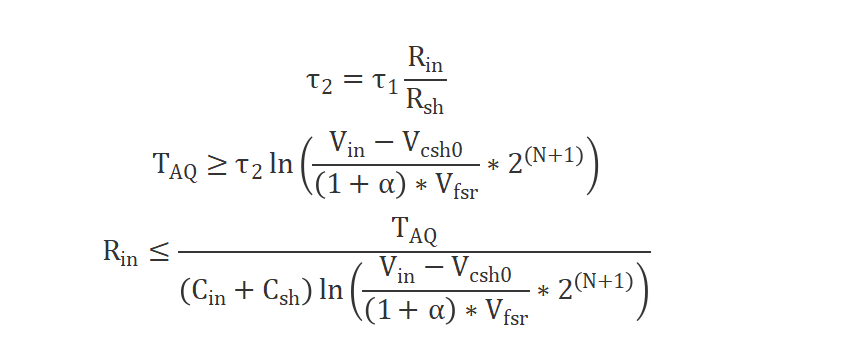

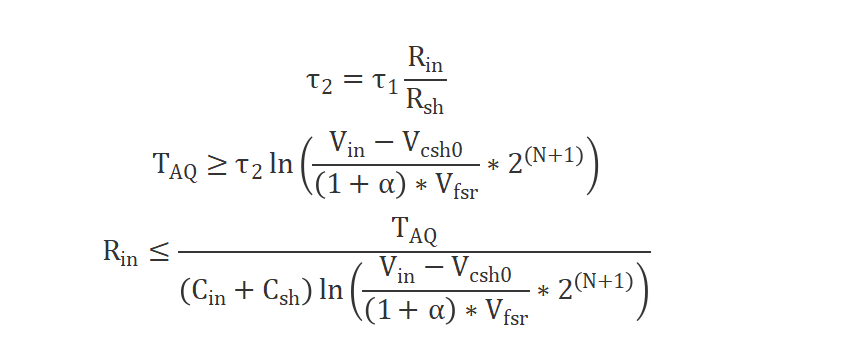

根據(jù)ADC內(nèi)部結(jié)構(gòu)和,我們可以很輕松的推導(dǎo)出,第二階段的時(shí)間遠(yuǎn)遠(yuǎn)大于第一階段的時(shí)間,同時(shí),我們也可以推導(dǎo)出,采樣時(shí)間和輸入電阻必須滿足:

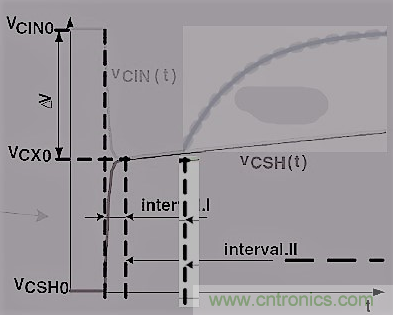

按照正常采樣,第二階段采樣時(shí)間必須要滿足輸入電阻、輸入電容和采樣電容并聯(lián)的乘積關(guān)系。如果采樣不足,又會(huì)出現(xiàn)怎樣的情況呢?在采樣開(kāi)關(guān)斷開(kāi)之后,采樣保持階段,由于Cx變小,輸入電容充電速度明顯加快,此時(shí),Csh電壓幾乎不變,大致波形應(yīng)如下(具體推導(dǎo)公式不再列出):

結(jié)合該客戶反饋的測(cè)試結(jié)果,我們大致判斷出,客戶這個(gè)問(wèn)題是由于在未達(dá)到采樣條件時(shí)就開(kāi)始進(jìn)行ADC采樣并轉(zhuǎn)換引起。

解決方案

結(jié)合上述電路模型及其推導(dǎo)公式,我們?cè)撊绾谓鉀Q此類(lèi)問(wèn)題呢?我們給出三種建議:

A. 延遲采樣時(shí)間;

B. 加大輸入電容;

C. 增加驅(qū)動(dòng)電路,重構(gòu)輸入阻抗。

實(shí)施細(xì)節(jié)

一、延遲采樣,增加采樣周期

這一點(diǎn)不難理解,只要采樣速率沒(méi)有要求,理論上來(lái)說(shuō),增加采樣周期,完成ADC轉(zhuǎn)換完全沒(méi)問(wèn)題,本文不做重點(diǎn)講解。

二、加大輸入電容

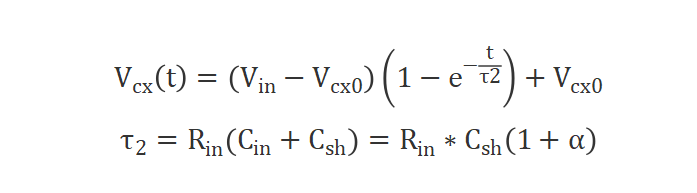

我們?cè)诤芏郃DC采樣場(chǎng)合都看到ADC輸入前端有一個(gè)電容,如果我們?cè)O(shè)定Rin非常小,忽略不計(jì),那么這個(gè)電容有何作用呢?本文中,我們有一個(gè)推導(dǎo)公式:

由于在每個(gè)采樣周期內(nèi),輸入電容和采樣電容的電壓值都會(huì)相對(duì)固定,如果我們通過(guò)調(diào)整輸入輸入電容和采樣電容的比值來(lái)調(diào)整第一階段的快速充電時(shí)間,這似乎不失為一個(gè)好辦法。

但是,當(dāng)輸入電源發(fā)生變化的時(shí)候,由于采樣電容吸收能力有限,采樣端輸入電容泄放又會(huì)遇到新的難題。同時(shí),對(duì)于高頻信號(hào)來(lái)說(shuō),電容越大,等效阻抗會(huì)更小。

所以,在采樣端引入輸入電容的時(shí)候,我們需要非常謹(jǐn)慎,這個(gè)電容大多數(shù)是用來(lái)做高頻分量濾波用的。

三、增加驅(qū)動(dòng)能力,重構(gòu)輸入阻抗

我們?cè)倩氐降?階段采樣時(shí)間這個(gè)公式:

如果我們能夠降低輸入阻抗,就會(huì)大大縮短采樣時(shí)間,目前增加驅(qū)動(dòng)有兩種主流方法:

第一種是用變壓器來(lái)做驅(qū)動(dòng)電路,這個(gè)方法有一個(gè)弱點(diǎn),只能針對(duì)交流信號(hào),對(duì)工作頻率有要求,需要做匹配設(shè)計(jì)。

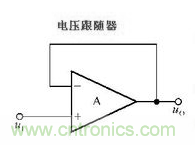

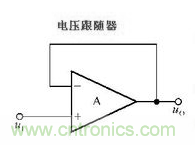

另一種方法是用運(yùn)放做跟隨器,這樣可以大大降低信號(hào)端的內(nèi)阻,大多數(shù)模擬前端都采用這種方法來(lái)做前端設(shè)計(jì)。

經(jīng)過(guò)和客戶確認(rèn),客戶后來(lái)采用運(yùn)放做跟隨驅(qū)動(dòng)的方法,重新測(cè)試一版,測(cè)試采樣端波形如下圖,從硬件電路來(lái)看,應(yīng)該找到問(wèn)題所在,目前還在驗(yàn)證中。

Microchip ADC介紹

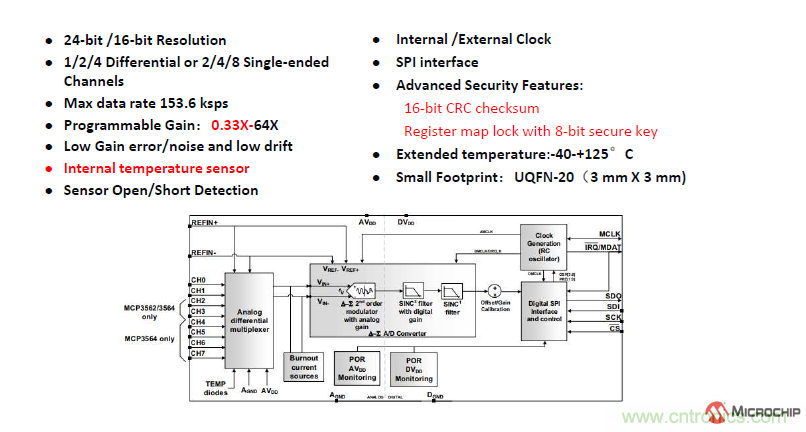

針對(duì)傳感器市場(chǎng),Microchip推出多種Delta-Sigma ADC,可以滿足多種不同應(yīng)用需求,特別是這么缺貨的年代,

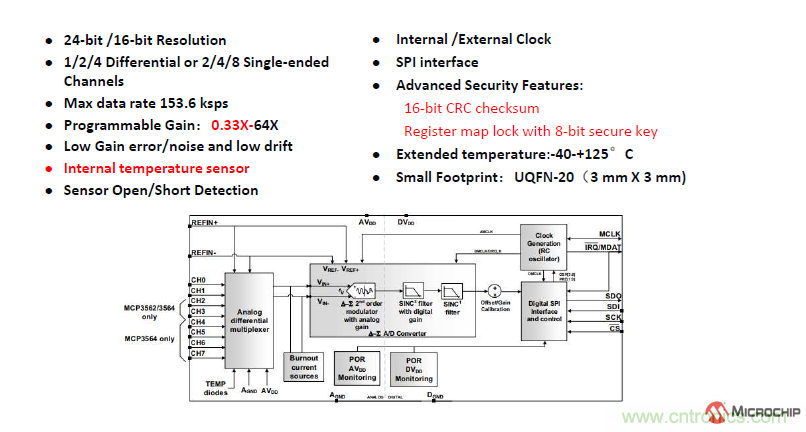

MCP356X簡(jiǎn)介:

24 bits Delta-Sigma ADC

153.6 kSPS @ 16 bits,19.2 kSPS @ 24 bits

OSR Rang:32-98034

VREF

External VREF rang:0.1V-AVDD

Clock Internal or External

RMS Effective Resolution: Up to 23.3 bits

Power Consumption:0.8-2 Ma

Package:UQFN-20同時(shí),Microchip也有多種運(yùn)算放大器可以用來(lái)做前端設(shè)計(jì),供大家選擇。

關(guān)于世健——亞太區(qū)領(lǐng)先的元器件授權(quán)代理商

世健是完整解決方案的供應(yīng)商,為亞洲電子廠商包括原設(shè)備生產(chǎn)商(OEM)、原設(shè)計(jì)生產(chǎn)商(ODM)和電子制造服務(wù)提供商(EMS)提供優(yōu)質(zhì)的元器件、工程設(shè)計(jì)及供應(yīng)鏈管理服務(wù)。

世健與供應(yīng)商及電子廠商緊密協(xié)作,為新的科技與趨勢(shì)作出定位,并幫助客戶把這些最先進(jìn)的科技揉合于他們的產(chǎn)品當(dāng)中。集團(tuán)分別在新加坡、中國(guó)及越南設(shè)有研發(fā)中心,專(zhuān)業(yè)的研發(fā)團(tuán)隊(duì)不斷創(chuàng)造新的解決方案,幫助客戶提高成本效益并縮短產(chǎn)品上市時(shí)間。世健研發(fā)的完整解決方案及參考設(shè)計(jì)可應(yīng)用于工業(yè)、無(wú)線通信及消費(fèi)電子等領(lǐng)域。

世健是新加坡的主板上市公司,總部設(shè)于新加坡,擁有約650名員工,業(yè)務(wù)范圍已擴(kuò)展至亞太區(qū)40多個(gè)城市和地區(qū),遍及新加坡、馬來(lái)西亞、泰國(guó)、越南、中國(guó)、印度、印度尼西亞、菲律賓及澳大利亞等十多個(gè)國(guó)家。世健集團(tuán)在2020年的年?duì)I業(yè)額超過(guò)11億美元。1993年,世健在香港設(shè)立區(qū)域總部——世健系統(tǒng)(香港)有限公司,正式開(kāi)始發(fā)展中國(guó)業(yè)務(wù)。目前,世健在中國(guó)擁有十多家分公司和辦事處,遍及中國(guó)主要大中型城市。憑借專(zhuān)業(yè)的研發(fā)團(tuán)隊(duì)、頂尖的現(xiàn)場(chǎng)應(yīng)用支持以及豐富的市場(chǎng)經(jīng)驗(yàn),世健在中國(guó)業(yè)內(nèi)享有領(lǐng)先地位。

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問(wèn)題,請(qǐng)電話或者郵箱聯(lián)系小編進(jìn)行侵刪。