【導(dǎo)讀】差分信號在高速電路設(shè)計中的應(yīng)用越來越廣泛,電路中最關(guān)鍵的信號往往都要采用差分結(jié)構(gòu)設(shè)計。本文將從LVDS信號仿真、設(shè)計等多方面探討合適的LVDS信號的實現(xiàn)。

隨著電子設(shè)計技術(shù)的不斷進步,要求更高速率信號的互連。在傳統(tǒng)并行同步數(shù)字信號的數(shù)位和速率將要達到極限的情況下,開始轉(zhuǎn)向從高速串行信號尋找出路。HyperTansport(by AMD), Infiniband(by Intel),PCI-Express(by Intel)等第三代I/O總線標(biāo)準(zhǔn)(3GI/O)不約而同地將低壓差分信號(LVDS)作為下一代高速信號電平標(biāo)準(zhǔn)。本文將從LVDS信號仿真、設(shè)計等多方面探討合適的LVDS信號的實現(xiàn)。

前 言

隨著近幾年對速率的要求快速提高,新的總線協(xié)議不斷的提出更高的速率。傳統(tǒng)的總線協(xié)議已經(jīng)不能夠滿足要求了。串行總線由于更好的抗干擾性,和更少的信號線,更高的速率獲得了眾多設(shè)計者的青睞。而串行總線又尤以差分信號的方式為最多。而在我們的項目中的PCI- Express串行信號線正采用了LVDS技術(shù)。所以以下的敘述中都以串行信號中LVDS信號為代表講述。

串行LVDS信號的PCB設(shè)計

1. 差分信號的概念和優(yōu)點

差分信號(Differential Signal)在高速電路設(shè)計中的應(yīng)用越來越廣泛,電路中最關(guān)鍵的信號往往都要采用差分結(jié)構(gòu)設(shè)計。何為差分信號?通俗地說,就是驅(qū)動端發(fā)送兩個等值、反相的信號,接收端通過比較這兩個電壓的差值來判斷邏輯狀態(tài)“0”還是“1”,而承載差分信號的那一對走線就稱為差分走線。差分信號與普通的單端信號走線相比,最明顯的優(yōu)勢體現(xiàn)在以下三個方面:

(1)抗干擾能力強。因為兩根差分走線之間的耦合很好,當(dāng)外界存在噪聲干擾時,幾乎是同時被耦合到兩條線上,而接收端關(guān)心的只是兩信號的差值,所以外界的共模噪聲可以被完全抵消。

(2)能有效抑制EMI。由于兩根信號的極性相反,他們對外輻射的電磁場可以相互抵消。耦合的越緊密,互相抵消的磁力線就越多。泄露到外界的電磁能量越少。

(3)時序定位精確。由于差分信號的開關(guān)變化是位于兩個信號的交點,而不像普通單端信號依靠高低兩個閥值電壓判斷,因而受工藝,溫度的影響小,能降低時序上的誤差,同時也更適合于低幅度信號的電路。目前流行的LVDS(low voltage differential signaling)就是指這種小振幅差分信號技術(shù)。

2. LVDS信號在PCB上的設(shè)計要點

LVDS信號被廣泛應(yīng)用于計算機、通信以及消費電子領(lǐng)域,并被以PCI-Express為代表的第三代I/O標(biāo)準(zhǔn)中采用,而在我們的項目中PCI-Express信號正是采用的是LVDS信號。LVDS信號不僅是差分信號,而且還是高速數(shù)字信號。因此LVDS傳輸媒質(zhì)不管使用的是PCB線還是電纜,都必須采取措施防止信號在媒質(zhì)終端發(fā)生反射,同時應(yīng)減少電磁干擾以保證信號的完整性。只要我們在布線時考慮到以上這些要素,設(shè)計高速差分線路板并不很困難。下面簡要介紹LVDS信號在PCB上的設(shè)計要點:

2.1布成多層板

有LVDS信號的電路板一般都要布成多層板。由于LVDS信號屬于高速信號,與其相鄰的層應(yīng)為地層,對LVDS信號進行屏蔽防止干擾。對于密度不是很大的板子,在物理空間條件允許的情況下,最好將LVDS信號與其它信號分別放在不同的層。例如,在四層板中,通??梢园匆韵逻M行布層:LVDS信號層、地層、電源層、其它信號層。

2.2 LVDS信號阻抗計算與控制。

LVDS信號的電壓擺幅只有350mV,適于電流驅(qū)動的差分信號方式工作。為了確保信號在傳輸線當(dāng)中傳播時不受反射信號的影響,LVDS信號要求傳輸線阻抗受控,通常差分阻抗為100 /-10Ω。阻抗控制的好壞直接影響信號完整性及延遲。如何對其進行阻抗控制呢?

(1)確定走線模式、參數(shù)及阻抗計算。LVDS分外層微帶線差分模式和內(nèi)層帶狀線差分模式。阻抗可以通過合理設(shè)置參數(shù),利用相關(guān)軟件計算得出。通過計算,阻抗值與絕緣層厚度成正比,與介電常數(shù)、導(dǎo)線的厚度及寬度成反比。

(2) 走平行等距線及緊耦合原則。確定走線線寬及間距后,在走線時嚴(yán)格按照計算出的線寬和間距,兩線的間距要一直保持不變,也就是要保持平行(可以放圖)。同時 在計算線寬和間距時最好遵守緊耦合的原則,也就是差分對線間距小于或等于線寬。當(dāng)兩條差分信號線距離很近時,電流傳輸方向相反,其磁場相互抵消,電場相互 耦合,電磁輻射也要小得多。而且要兩條線走在同一層,避免分層走線。因為在PCB板的實際加工過程中,由于層疊之間的層壓對精確度大大低于同層蝕刻精度,以及層壓過程中的介質(zhì)流失,不能保證差分線的間距等于層間介質(zhì)厚度,會造成層間差分對的差分阻抗變化。

(3)走短線、直線。為確保信號的質(zhì)量,LVDS差分對走線應(yīng)該盡可能地短而直,減少布線中的過孔數(shù),避免差分對布線太長,出現(xiàn)太多的拐彎,拐彎處盡量用45°或弧線,避免90°拐彎。

2.3不同差分線對間處理

LVDS對走線方式的選擇沒有限制,微帶線和和帶狀線均可,但是必須注意要有良好的參考平面。對不同差分線之間的間距要求間隔不能太小,至少應(yīng)大于3-5倍差分線間距。必要時在不同差分線對之間加地孔隔離以防止相互間的串?dāng)_。LVDS信號盡量遠離其它信號。LVDS差分信號不可以跨平面分割。盡管兩根差分信號互為回流路徑,跨分割不會割斷信號的回流,但是跨分割部分的傳輸線會因為缺少參考平面而導(dǎo)致阻抗的不連續(xù)(如圖所示,其中GND1、GND2為LVDS相鄰的地平面)。

圖1:差分對線

接收端的匹配電阻的布局。對接收端的匹配電阻到接收管腳的距離要盡量靠近。同時匹配電阻的精度要控制。對于點到點的拓撲,走線的阻抗通常控制在100Ω,但匹配電阻可以根據(jù)實際的情況進行調(diào)整。電阻的精確度最好是1%-2%。因為根據(jù)經(jīng)驗,10%的阻抗不匹配就會產(chǎn)生5%的反射。

串行LVDS信號的仿真分析

以上分析了LVDS信號設(shè)計時必須注意的事項,雖然在PCB設(shè)計的時候一般都會遵守以上的規(guī)則進行,但是為了能夠提高設(shè)計的正確性和準(zhǔn)確行必須對PCB進行信號完整行仿真,通過仿真得到信號的串?dāng)_、延時、反射和眼圖波形,從而達到設(shè)計即正確的目標(biāo)。信 號完整性問題的仿真流程是先建立元器件的仿真模型,然后進行前仿真確定布線過程的參數(shù)和約束條件,物理實現(xiàn)階段按照約束條件進行設(shè)計,最后進行后仿真,驗 證設(shè)計是否滿足設(shè)計要求。在整個流程中模型的精確性直接影響仿真的結(jié)果,而在前仿真和后仿真階段用到的仿真分析方法對于仿真結(jié)果同樣至關(guān)重要,而在本設(shè)計 中采用了精確度較高的spice模型。下面結(jié)合實際的項目來說明仿真在本設(shè)計的實施過程。

3.1. PCB疊層設(shè)置

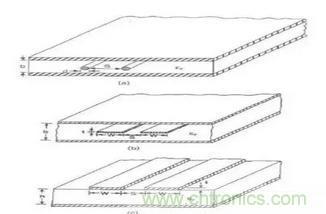

由上面的分析知道,PCB板的疊層設(shè)置和信號的耦合以及阻抗計算都有著密切的關(guān)系,所以在開始PCB設(shè)計之前必須進行疊層設(shè)計,然后進行信號的阻抗計算。在本設(shè)計中的疊層設(shè)計見下圖:

圖2:疊層設(shè)計

由于PCB密度較高,本設(shè)計采用10層板的疊層結(jié)構(gòu),經(jīng)過合理的安排疊層厚度,通過allegro計算,表面微帶和內(nèi)層帶狀線的差分線在線寬6㏕線間距6㏕時,阻抗理論計算值分別為100.1和98.8Ω。符合阻抗控制要求。

3.2. 設(shè)置直流電壓值

這一步驟主要是為某些特定的網(wǎng)絡(luò)(一般是電源地等)指定其直流電壓值,確定DC電壓加在網(wǎng)絡(luò)上,執(zhí)行EMI仿真需要確定一個或多個電壓源管腳,這些電壓值包涵了模型在仿真過程中使用的參考電壓信息。

3.3. 器件設(shè)置

在allegro仿真的時候allegro會把器件分成三大類:IC、連接器和分立器件(電阻電容等),allegro會依據(jù)器件類型來給器件的管腳分配仿真屬性,分立器件和連接器的管腳屬性為UPSPEC,而IC的管腳屬性可以為IN、OUT和BI等。

3.4. 模型分配

在板級高速PCB仿真過程中主要用要的模型有器件模型和傳輸線模型。器件模型一般是由器件生產(chǎn)廠家提供的。在高速串行信號中,我們采用的是精度更高的SPICE模型來進行仿真分析。傳輸線模型則是通過仿真軟件建模形成的。信號在傳輸時,傳輸線會使得信號完整性問題突出,因此仿真軟件對傳輸線精確建模的能力直接影響仿真結(jié)果。

圖3:差分對線模型b:帶狀線 c: 微帶線

而 信號路徑和返回路徑所在的傳輸線不可能是理想的導(dǎo)體,因此它們都有有限的電阻,電阻的大小由傳輸線的長度和橫截面積決定。任何傳輸線都可以劃分為一系列串 接線段。同樣的在傳輸線之間的介質(zhì)也不可能是理想的絕緣體,漏電流總是存在的。實際的傳輸線模型由無數(shù)個短線段組成,短線段的長度趨于零。 關(guān)于傳輸線的模型是allegro自動分配的。仿真的時候主要是分配器件模型。

3.5. SI檢查

SI Audit功能是用來檢查某一個特殊的網(wǎng)絡(luò)或者一群網(wǎng)絡(luò)是否能夠被提取出來進行分析,一般就是設(shè)置我們需要關(guān)注的高速網(wǎng)絡(luò),本設(shè)計主要關(guān)注LVDS串行信號。

3.6.提取網(wǎng)絡(luò)拓撲

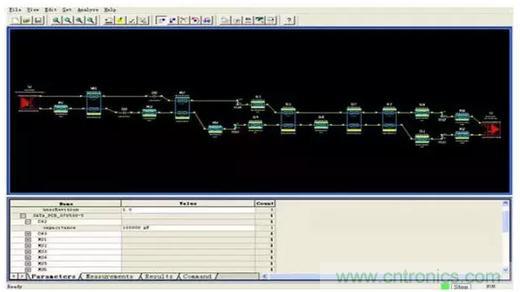

從PCB中提取待關(guān)注信號的拓撲結(jié)構(gòu),一般包括驅(qū)動端和接收端,以及傳輸線和相關(guān)的匹配電阻電容等,可以從拓撲結(jié)構(gòu)中看出該網(wǎng)絡(luò)經(jīng)過那些路徑,那些會對信號的傳輸造成影響。本文僅以其中一個信號的網(wǎng)絡(luò)拓撲圖為例,如圖4所示:

圖4:差分對線的網(wǎng)絡(luò)拓撲

3.7. 查看波形

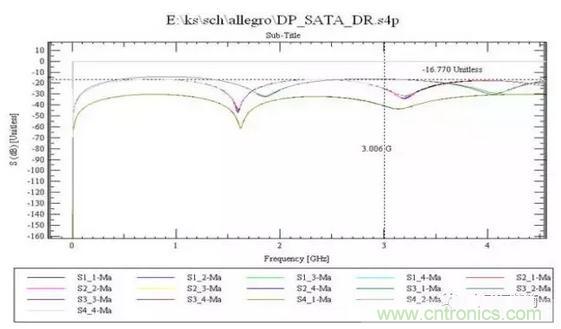

以上的相關(guān)步驟設(shè)置好以后就可以進行仿真了,allegro可以進行信號的反射仿真、串?dāng)_仿真,差分線還要進行眼圖分析。當(dāng)然仿真也分前仿真和后仿真,在利用allegro進行PCB設(shè)計的時候還需要結(jié)合仿真的結(jié)果實時的對設(shè)計進行修改以達到符合要求的目的。由于仿真過程復(fù)雜,步驟繁瑣,在此不一一進行描述, 差分對的布線有兩點要注意,一是兩條線的長度要盡量一樣長,等長是為了保證兩個差分信號時刻保持相反極性,減少共模分量。另一是兩線的間距(此間距由差分阻抗決定)要一直保持不變,也就是要保持平行。平行的方式有兩種,一為兩條線走在同一走線層(side-by-side),一為兩條線走在上下相鄰兩層(over-under)。一般以前者side-by-side 實現(xiàn)的方式較多。等距則主要是為了保證兩者差分阻抗一致,減少反射。對差分對的布線方式應(yīng)該要適當(dāng)?shù)目拷移叫小K^適當(dāng)?shù)目拷且驗檫@間距會影響到差分阻抗(differential impedance)的值, 此值是設(shè)計差分對的重要參數(shù)。需要平行也是因為要保持差分阻抗的一致性。若兩線忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal integrity)及時間延遲(timing delay)。從仿真的S參數(shù)曲線圖可以分析差分對的差分阻抗(differential impedance),以及信號完整性。下面給出本設(shè)計中的關(guān)鍵信號仿真波形以供加以說明。 從仿真圖例圖5看到,S11在0-3.0GHz 的頻域范圍內(nèi)其最劣化的指標(biāo)為:-16.770db以下 ,S22(粉紅色的曲線)也不劣于-17db。 這說明該差分對的差分阻抗(differential impedance)接近設(shè)計指標(biāo),信號完整性得到了保證。

圖5:差分對線仿真S參數(shù)曲線

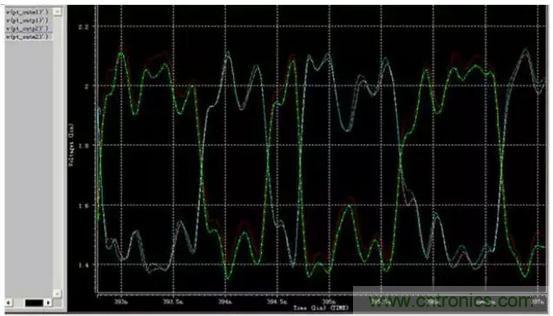

圖6:差分對IN,OUT的HSPICE仿真圖

通過差分對IN,OUT的HSPICE仿真,圖6顯示的結(jié)果:差分對線的對稱良好。

結(jié)論 通過以上的仿真分析可知,在PCB的設(shè)計階段對于高速LVDS信號的各項要求都能達到,而經(jīng)過實際的PCB生產(chǎn)也證明了該設(shè)計的正確性,該產(chǎn)品運行穩(wěn)定,完全能達到PCI-express高速數(shù)據(jù)傳輸?shù)囊?,可靠性高。?本文的分析可知,在高速串行信號的設(shè)計中,不僅考慮電路設(shè)計,其板圖設(shè)計和仿真分析也同樣的重要,而且隨著信號的頻率越來越大,影響信號的延時、串?dāng)_、信 號完整性等的因素越來越復(fù)雜。同時控制這些因素的影響也越來越困難,工程師必須深入的分析布線設(shè)計、借助精確的模型、有效的仿真和科學(xué)的分析方法,才能給 復(fù)雜的高速設(shè)計以正確的指導(dǎo),減少修正周期確保設(shè)計成功。