【導(dǎo)讀】一種特殊形式的運(yùn)算放大器,適用于精密應(yīng)用,在這些應(yīng)用中,輸入差分信號非常小,輸入引腳上的任何偏移都可能在輸出端引起嚴(yán)重誤差。

零漂移運(yùn)算放大器

一種特殊形式的運(yùn)算放大器,適用于精密應(yīng)用,在這些應(yīng)用中,輸入差分信號非常小,輸入引腳上的任何偏移都可能在輸出端引起嚴(yán)重誤差。

這些專用運(yùn)算放大器除了具有低輸入失調(diào)電壓外,通常還在寬溫度和時間范圍內(nèi)具有高共模抑制比(CMRR)、高電源抑制比(PSRR)、高開環(huán)增益和較低的漂移。所有這些特性使它們成為精密應(yīng)用的理想選擇,因?yàn)檫@些器件能夠精確地測量小的差分電壓,并且高開環(huán)增益確保良好的閉環(huán)增益精度。它們也不太容易受到外界如電源變化、共模電壓和溫度效應(yīng)的影響。

零漂移運(yùn)算放大器特別適合于差分信號較小的精密應(yīng)用,尤其是低頻應(yīng)用。這包括物聯(lián)網(wǎng)(IoT)和工業(yè)4.0應(yīng)用(工業(yè)物聯(lián)網(wǎng)IoT)中使用的許多感知方案。

隨著在電池供電(或能量采集)應(yīng)用中趨向使用低功耗、節(jié)能傳感器,零漂移運(yùn)算放大器在許多現(xiàn)代應(yīng)用中尤其有用,如現(xiàn)在正迅速增長的IoT。

(一)輸入偏置電壓

輸入失調(diào)電壓是個重要參數(shù),因?yàn)樗x了可以捕獲和放大的最小信號,從而限定了較低的動態(tài)范圍。在數(shù)據(jù)表中,通常將其稱為VOS或VIO。它是IN+和IN-端子之間差分電壓的量度,有效地測量了運(yùn)算放大器輸入對的匹配程度。

在理論上理想的運(yùn)算放大器中,輸入端子在閉環(huán)系統(tǒng)中將處于相同的電壓電平。但在實(shí)際應(yīng)用中,總會有一些輸入失調(diào)電壓,不過很小。這是由于半導(dǎo)體材料的實(shí)際變化導(dǎo)致輸入引腳上的內(nèi)部電壓升高。這些材料差異還會導(dǎo)致輸入失調(diào)電壓隨溫度變化而產(chǎn)生幅度變化甚至極性變化,使應(yīng)用中的校準(zhǔn)極具挑戰(zhàn)性。

典型的通用運(yùn)算放大器的輸入失調(diào)電壓約為幾毫伏,而專用零漂移運(yùn)算放大器的輸入失調(diào)電壓約為10-25微伏,小兩個數(shù)量級。

(二)零漂移技術(shù)和架構(gòu)

可采用幾種技術(shù)來確保在寬廣的溫度和時間范圍內(nèi)具有低輸入失調(diào)電壓,以產(chǎn)生零漂移運(yùn)算放大器。實(shí)現(xiàn)此目標(biāo)的方法之一是定期測量輸入失調(diào)電壓,然后施加校正電壓以調(diào)整運(yùn)算放大輸出的偏移量。這種方法被稱為“斬波穩(wěn)定”,因其在前饋部分使用了斬波器。

斬波穩(wěn)定技術(shù)的主要限制在于斬波器的電路中包含時鐘系統(tǒng)。因此,零漂移運(yùn)算放大器易受經(jīng)典采樣系統(tǒng)混疊或外差問題的影響。當(dāng)輸入信號的頻率類似于斬波電路的時鐘頻率時,這尤為明顯。斬波穩(wěn)定運(yùn)算放大器的最佳性能出現(xiàn)在輸入信號頻率保持在相關(guān)奈奎斯特頻率以下時。設(shè)計人員應(yīng)注意確保輸入頻率保持在失調(diào)校正頻率的一半以下(并在閉環(huán)帶寬內(nèi)),以獲得最佳性能。

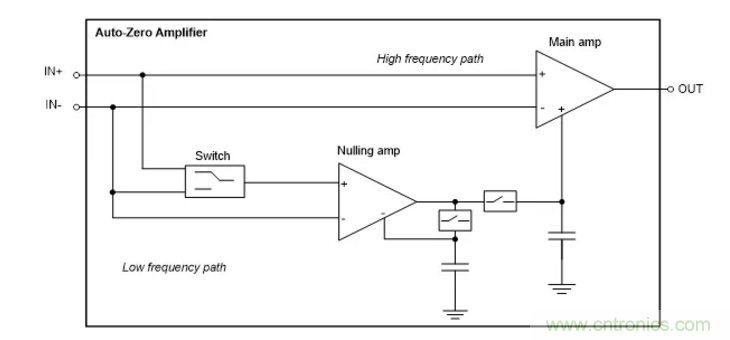

創(chuàng)建零漂移架構(gòu)的另一種方法稱為“自動歸零”。盡管系統(tǒng)架構(gòu)最初看起來類似于具有高頻路徑和低頻前饋校正路徑的斬波穩(wěn)定架構(gòu),但實(shí)現(xiàn)方式卻大不相同。

雖然所有斬波穩(wěn)定和自動歸零運(yùn)算放大器都易受混疊影響,但可以減輕這種影響。例如,安森美半導(dǎo)體的NCS333和NCS21911器件含兩個級聯(lián)對稱型RC陷波濾波器,這些濾波器已調(diào)諧到斬波頻率和5次諧波。與市場上的其他器件相比,這種布置能夠減小混疊效應(yīng),并提供強(qiáng)大的性能。

(三)采用零漂移運(yùn)算放大器設(shè)計的注意事項

使用零漂移運(yùn)算放大器的主要設(shè)計考慮因素涉及減輕混疊。這現(xiàn)象不應(yīng)被認(rèn)為是一種缺陷,這是需要了解和緩解的現(xiàn)象。

減輕混疊的關(guān)鍵是知道運(yùn)算放大器的時鐘頻率。在許多情況下,制造商不會發(fā)布信息,因此需要進(jìn)行實(shí)驗(yàn)以推斷。最簡單和最有效的一個方法是簡單的時域測試,同時使用示波器監(jiān)視輸出。合理地假設(shè)頻率在器件的增益帶寬積之內(nèi),則放大器輸入應(yīng)從零頻率掃描到增益帶寬積。測試表明,時鐘頻率通常是增益帶寬積的三分之一,但并非總是如此。

為從零漂移放大器獲得最佳性能,設(shè)計人員應(yīng)遵循奈奎斯特采樣理論,并確保最大信號頻率小于內(nèi)部時鐘頻率的一半。但精密模擬電路對從雜散信號、噪聲或紋波中拾取敏感,其中任何一個都可能包含高于奈奎斯特頻率的頻率,這可能會導(dǎo)致誤差或錯誤的輸出。

好的做法是在放大器之前加入一個模擬低通濾波器,以用作抗混疊濾波器。濾波器衰減高于奈奎斯特頻率的頻率以減少或消除任何混疊。該濾波器必須是純模擬的并且沒有有源元件。在許多情況下,只需要一個簡單的兩段級聯(lián)RC濾波器。

一般而言,級聯(lián)零漂移放大器并不是好的設(shè)計實(shí)踐,因?yàn)椴煌臅r鐘頻率可能會相互作用,從而導(dǎo)致不良影響,包括可能的混疊。建議使用相對較低值的輸入電阻,因?yàn)閿夭ǚ€(wěn)定電路會產(chǎn)生輸入電流尖峰,從而產(chǎn)生電壓,電壓隨后被放大。如前所述,可使用合適的無源RC濾波器來衰減這些尖峰。

設(shè)計人員還應(yīng)意識到,零漂移運(yùn)算放大器的建立時間有限,因?yàn)閿夭娐肥腔跁r間的采樣。這意味著輸入的大動態(tài)步長(或過載)可能使環(huán)路需要時間來重新建立低輸入失調(diào)。但通過使用更高的時鐘頻率,可以期望快速恢復(fù)和建立,通常在幾十微秒之內(nèi)。任何事情都需要權(quán)衡取舍,在這也不例外,因?yàn)楦斓慕⑺俣瓤赡軐?dǎo)致更高的輸入失調(diào)。大多數(shù)零漂移運(yùn)算放大器都優(yōu)先在建立時間內(nèi)減小輸入失調(diào)。

由于在零漂移運(yùn)算放大器內(nèi)有相當(dāng)數(shù)量的邏輯電路,啟動所需的時間是有限的,在此期間,輸出將反映未經(jīng)校正的輸入失調(diào)電壓。在大多數(shù)情況下,這不是個問題,因?yàn)橛绊懼话l(fā)生在最初的幾個時鐘周期,而相關(guān)的時間是在整個系統(tǒng)的上電時間內(nèi)。

如果設(shè)計人員使用仿真工具來開發(fā)電路,應(yīng)意識到SPICE模型不能深入了解零漂移行為,如混疊。典型的SPICE模型能夠模擬設(shè)備的線性性能,而不是斬波器的性能,部分原因是這會降低模擬的速度。

(四)小結(jié)

輸入失調(diào)電壓是所有運(yùn)算放大器的一個關(guān)鍵參數(shù),對于看重此參數(shù)的應(yīng)用,可采用專用的零漂移運(yùn)算放大器,實(shí)現(xiàn)在低差分輸入情況下的精密應(yīng)用。就像所有的工程方案,設(shè)計人員需要權(quán)衡取舍以獲得最佳性能。而這些專用器件使輸入頻率保持在奈奎斯特頻率以下,并提供一些基本的無源濾波,極其適用于低頻傳感器應(yīng)用。

圖1:斬波穩(wěn)定運(yùn)算放大器的簡化框圖

圖2:自動歸零運(yùn)算放大器的簡化框圖

(來源:安森美半導(dǎo)體 ,作者:Farhana Sarder)

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問題,請聯(lián)系小編進(jìn)行處理。