【導(dǎo)讀】要想獲得成功的FPGA的電路板,最關(guān)鍵的步驟就是需要低電壓電路,并且不止一個,行業(yè)普遍的都是四到五個,那么如何設(shè)計這四至五個不同的低壓電源對不同元件供電電路呢?

對于基于FPGA的電路板而言,需要四至五個不同的低壓電源對不同元件供電在現(xiàn)已經(jīng)非常普遍。從最開始的3.3V,然后逐步降至2.5V、1.8V、1.5V,現(xiàn)在的低壓僅為1.2V。每個新一代FPGA似乎都需要一個新的低電源電壓。除此之外,新的通信和內(nèi)存技術(shù)還需要額外的新I/O電源電壓和終端電壓?,F(xiàn)在,基于FPGA的電路板經(jīng)常需要四至五個不同的低電壓來為不同的元件供電。

同時,CMOS門數(shù)的增加和時鐘速度的提高導(dǎo)致了功率要求的提高。例如,Altera公司在其FPGA的Stratix/Stratix GX產(chǎn)品系統(tǒng)中提供了14個不同產(chǎn)品。在所需的功率方面,100 MHz下最小的FPGA時鐘所需的核心邏輯的峰值功率小于1.5 W,然而當(dāng)時鐘速度為300 MHz時,最大的FPGA時鐘所需的核心邏輯的峰值功率卻將近21W。這些趨勢使電路板設(shè)計者不得不使用更多而且性能更好的電源。值得慶幸的是,最新一代的低壓電源管理IC完全能夠滿足這些高性能電路板提出的要求。

實際應(yīng)用的電路

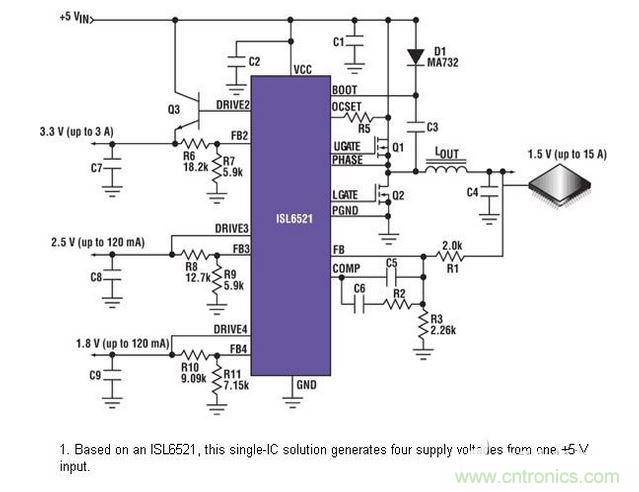

圖 1顯示了用于從+5V輸入產(chǎn)生四個電源電壓的單芯片解決方案。ISL6521($1.5625)同步降壓調(diào)節(jié)器包括三個線性調(diào)節(jié)器/控制器,它可以給電路板提供額外的電壓。120mA以下的I/O和IAUX電流可以直接從線性調(diào)節(jié)器輸出管腳(如圖所示的2.5V和1.8V)提供。另外,它們還可以用來控制外部晶體管。所有輸出電壓都可以使用電阻分壓器進(jìn)行全面調(diào)整。

ISL6521

在接通輸入電源時會自動初始化。通電重設(shè)(POR)功能會繼續(xù)監(jiān)視VCC管腳處的輸入偏置電源,POR功能會在偏置電源電壓超過其POR閾值時初始化軟啟動操作。所有電壓都會在不超過40ms單調(diào)降低,這通常是FPGA的要求。電流IC和模塊技術(shù)可以在單個IC上的每個輸出之間或者在單個封裝內(nèi)獲得非常好的隔離。板級電源耦合很可能是因為外部元件的選擇不佳和布局錯誤,而不在于兩個電源共享一個IC。本示例假設(shè)有一個+5V的電源,所選的FPGA需要在電流為2A時核心電壓為1.2V。根據(jù)幾個基本降壓轉(zhuǎn)換器原則來選擇開關(guān)元件以支持 FPGA核心啟動。首先,產(chǎn)生想要的輸出電壓所需的工作周期取決于最大開關(guān)調(diào)節(jié)器IC。降壓轉(zhuǎn)換器的工作周期(d)定義為:d=VOUT/VIN (1)

針對這個設(shè)計示例,得到的工作周期是24%。 ISL6521支持工作周期在0%至100%范圍內(nèi)的操作,但是輸出電壓范圍限制在0.8V至4.5V之間。不是所有控制器都支持整個工作周期范圍,當(dāng)處理電壓為輸出電壓范圍的兩極端值時的負(fù)載瞬態(tài)時,這個問題就出現(xiàn)了。FPGA 核心電壓對準(zhǔn)確性的要求視產(chǎn)品系列和提供商而不同。本示例假設(shè)FPGA核心電壓的所需準(zhǔn)確度為+5%或者電壓為60mV,這也是標(biāo)準(zhǔn)情況。該電壓應(yīng)與控制器的輸出電壓調(diào)節(jié)(2%或者24mV)進(jìn)行比較。如果控制器IC的輸出電壓調(diào)節(jié)大于FPGA的核心電壓所需的準(zhǔn)確度,則該控制器無法滿足FPGA要求。FPGA所需的準(zhǔn)確度和PWM的輸出電壓調(diào)節(jié)之差使得輸出電壓窗口能夠支持開關(guān)電源的輸出電壓脈動和允許的瞬態(tài)偏差。

這個示例中,電壓窗口為36mV。接下來選擇峰到峰輸出電壓脈動,選定一個合理的值10mV。輸出電壓脈動必須落在所計算出的電壓窗口內(nèi),或者需要一個調(diào)節(jié)容差較小的控制器。選擇較大的輸出電感器或較低的等效串聯(lián)電阻(ESR)輸出電容器可以減小輸出電壓脈動。