【導(dǎo)讀】在"電源系統(tǒng)優(yōu)化"系列文章的 第1部分 �,我們介紹了如何量化電源噪聲靈敏度��,以及如何將這些量值與信號鏈中產(chǎn)生的實際影響聯(lián)系起來���。有人問到:高性能模擬信號處理器件要實現(xiàn)出色性能���,真正的噪聲限值是多少?噪聲只是設(shè)計配電網(wǎng)絡(luò)(PDN)時的一個可測量的參數(shù)��。如 第1部分所述����,如果單純只是最小化噪聲,可能需要以增大尺寸��、提高成本或者降低效率為代價����。優(yōu)化配電網(wǎng)絡(luò)可以改善這些參數(shù),同時將噪聲降低到必要的水平��。

本文在闡述高性能信號鏈中電源紋波的影響的基礎(chǔ)上進一步分析���。我們將深入探討如何優(yōu)化高速數(shù)據(jù)轉(zhuǎn)換器的配電網(wǎng)絡(luò)����。

我們將對標準PDN與經(jīng)過優(yōu)化的PDN進行比較����,了解在哪些方面可以實現(xiàn)空間、時間和成本優(yōu)化���。后續(xù)文章將探討適合其他信號鏈器件(例如RF收發(fā)器)的特定優(yōu)化解決方案��。

AD9175雙通道12.6 GSPS高速數(shù)模轉(zhuǎn)換器的電源系統(tǒng)優(yōu)化

AD9175 是一款高性能����、雙通道�、16位數(shù)模轉(zhuǎn)換器(DAC),支持高達12.6 GSPS的DAC采樣速率�。該器件具有8通道、15.4 Gbps JESD204B數(shù)據(jù)輸入端口���、高性能片內(nèi)DAC時鐘倍頻器和數(shù)字信號處理功能��,適合單頻段和多頻段直接至射頻(RF)無線應(yīng)用���。

圖1.集成在現(xiàn)成評估板上的AD9175高速DAC的標準PDN��。

我們來看看如何為這個雙通道高速DAC優(yōu)化PDN����。圖1顯示安裝在現(xiàn)成評估板上的AD9175高速DAC的標準配電網(wǎng)絡(luò)����。該PDN由一個ADP5054分立式四通道開關(guān)和三個低壓降(LDO)后置穩(wěn)壓器構(gòu)成。旨在驗證是否可以改進和簡化該PDN�����,同時確保其輸出噪聲不會導(dǎo)致DAC性能大幅下降���。

AD9175需要8個電源軌���,可以分為4組,分別是:

● 1 V模擬(2個電源軌)

● 1 V數(shù)字(3個電源軌)

● 1.8 V模擬(2個電源軌)

● 1.8 V數(shù)字(1個電源軌)

分析:噪聲要求

在我們實施優(yōu)化之前�����,必須先了解這些電源軌的電源靈敏度����。我們將重點討論模擬電源軌,因為相比數(shù)字電源軌���,它們對噪聲更加敏感�����。

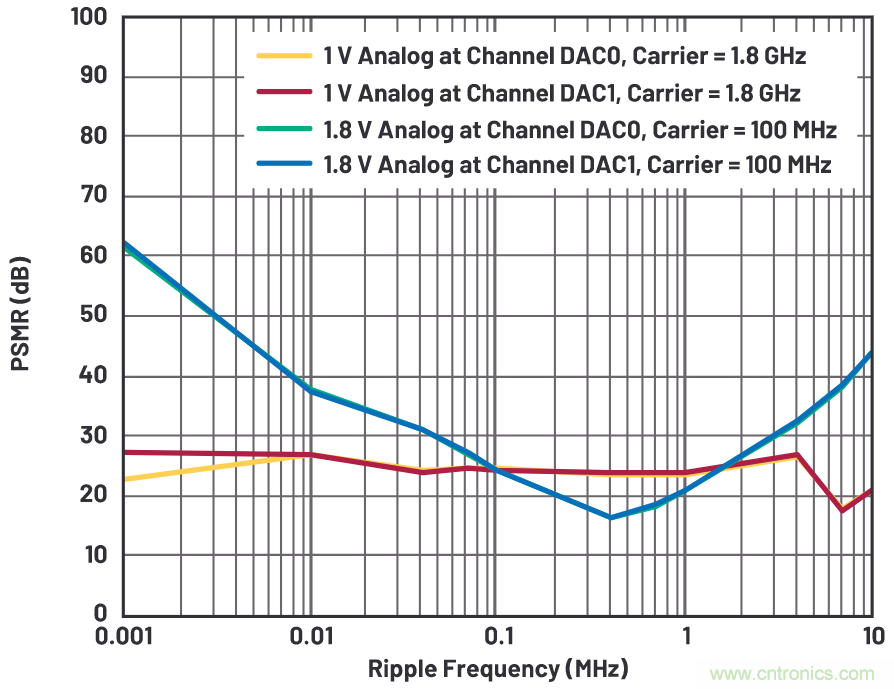

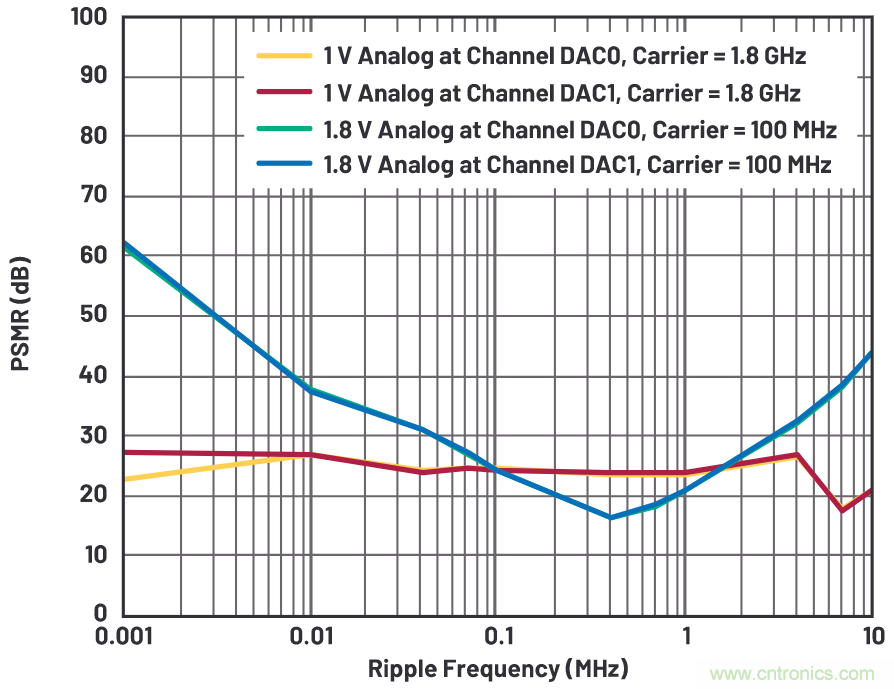

模擬電源軌的電源調(diào)制比(PSMR)如圖2所示��。注意����,1 V模擬電源軌在1/f頻率區(qū)域內(nèi)較為敏感�,而1.8 V模擬電源軌在開關(guān)轉(zhuǎn)換器的工作頻率范圍(100 kHz至約1 MHz)內(nèi)更敏感。

圖2.1 V模擬電源軌和1.8 V模擬電源軌上的AD9175高速DAC PSMR�。

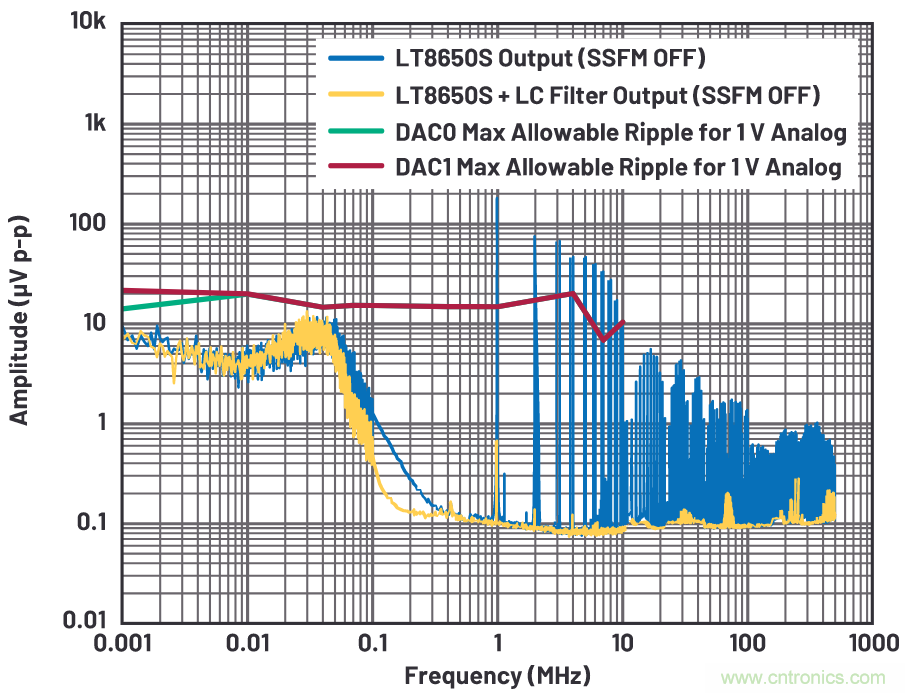

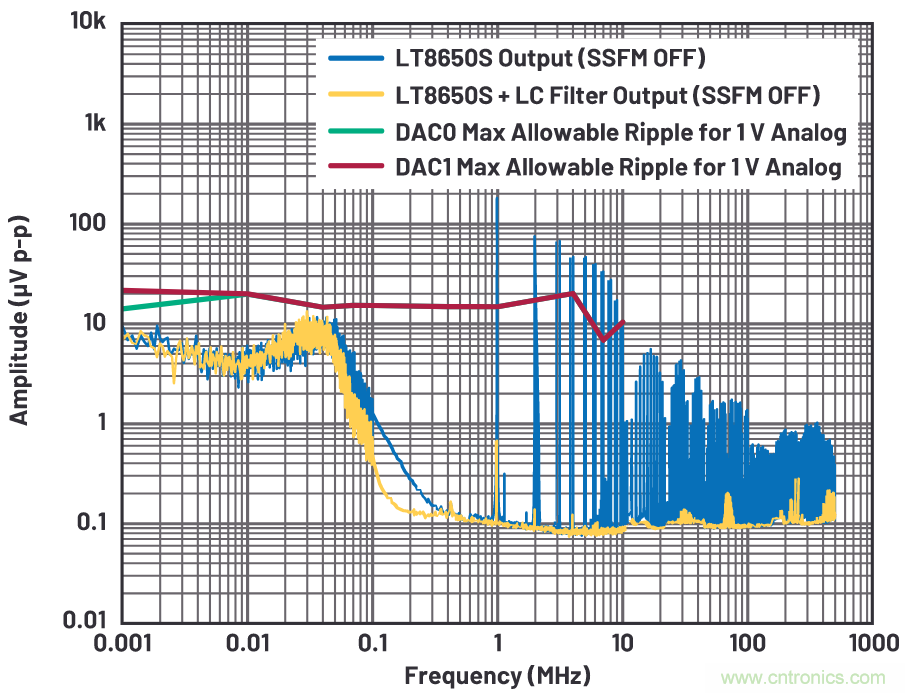

一種優(yōu)化方法是使用帶有LC濾波器的低噪聲開關(guān)穩(wěn)壓器。圖3顯示 LT8650S Silent Switcher®穩(wěn)壓器(帶和不帶LC濾波器)在展頻(SSFM)模式關(guān)閉時的傳導(dǎo)頻譜輸出�����。如 第1部分所述,SSFM可以降低開關(guān)頻率噪聲幅度�����,但會因為三角調(diào)制頻率在1/f區(qū)域產(chǎn)生噪聲峰值����。由于1/f噪聲已小幅偏離該閾值,增加的噪聲可能超過此電源軌的最大允許紋波閾值���。因此����,不建議在這種情況下使用SSFM�。最大允許電壓紋波閾值代表電源紋波電平,當(dāng)超過該值時����,DAC載波信號中的邊帶雜散將出現(xiàn)在DAC輸出頻譜的1 µV p-p本底噪聲上方。

從這些結(jié)果可以看出���,開關(guān)穩(wěn)壓器的1/f噪聲沒有超過1 V模擬電源軌的最大允許紋波閾值���。此外�����,LC濾波器足以將LT8650S的基本開關(guān)紋波和諧波降至最大允許紋波閾值以下。

圖3.LT8650S傳導(dǎo)頻譜輸出與1 V模擬電源軌的最大允許紋波閾值之間的關(guān)系���。

圖4顯示 LT8653S (帶和不帶LC濾波器)的傳導(dǎo)頻譜輸出�。如圖所示����,1.8 V電源軌的最大允許電壓紋波不會在AD9175輸出頻譜的1 µV p-p本底噪聲內(nèi)產(chǎn)生雜散?��?梢钥闯?���,LT8653S的1/f噪聲沒有超過最大允許紋波閾值�����,LC濾波器足以將LT8653S的基本開關(guān)紋波和諧波降至最大允許紋波閾值以下�����。

圖4.LT8653S傳導(dǎo)頻譜輸出與1.8 V模擬電源軌的最大允許紋波閾值之間的關(guān)系。

結(jié)果:優(yōu)化PDN

圖5顯示AD9175的優(yōu)化配電網(wǎng)絡(luò)����。旨在提高效率,降低空間要求以及圖1中PDN的功率損耗����,同時實現(xiàn)AD9175出色的動態(tài)性能。噪聲目標是基于圖3和圖4所示的最大允許波紋閾值��。

優(yōu)化的配電網(wǎng)絡(luò)由LT8650S和LT8653S Silent Switcher穩(wěn)壓器�,以及模擬電源軌上的LC濾波器構(gòu)成。在這個PDN中����,1 V模擬電源軌由LT8650S的VOUT1供電,LT8650S后接LC濾波器��;1 V數(shù)字電源軌直接由同一個LT8650S的VOUT2供電�,其后無需連接LC濾波器。對于AD9175���,其數(shù)字電源軌對電源噪聲不太敏感��,因此可以在不降低DAC動態(tài)性能的情況下直接為這些電源軌供電��。帶有LC濾波器的LT8653S直接為1.8 V模擬和1.8 V數(shù)字電源軌供電����。

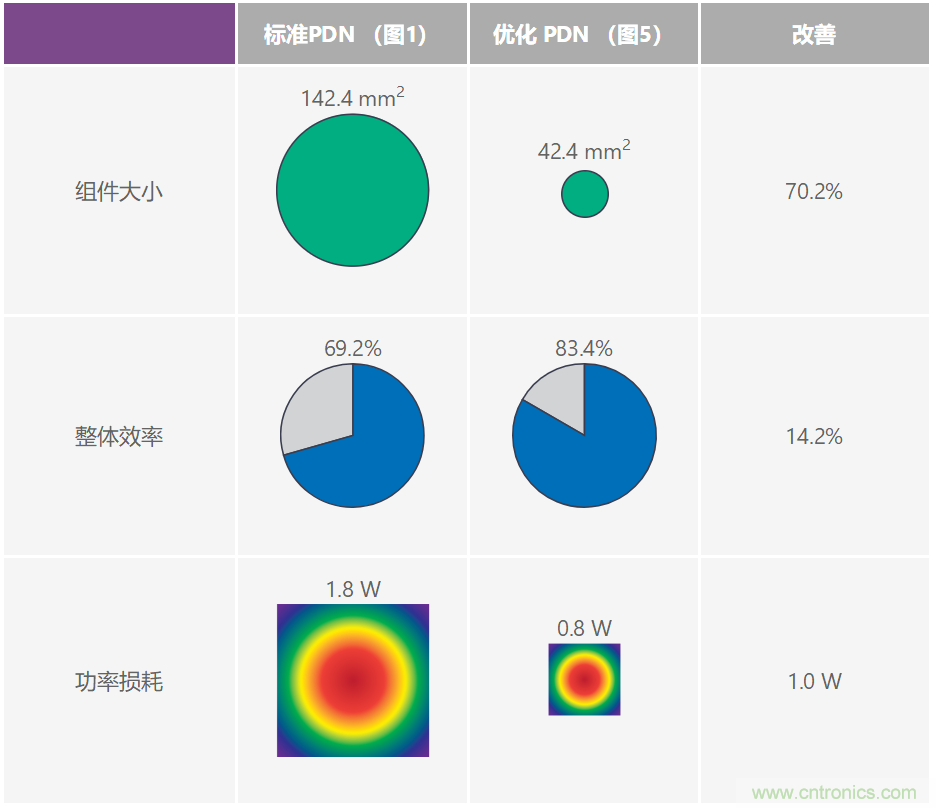

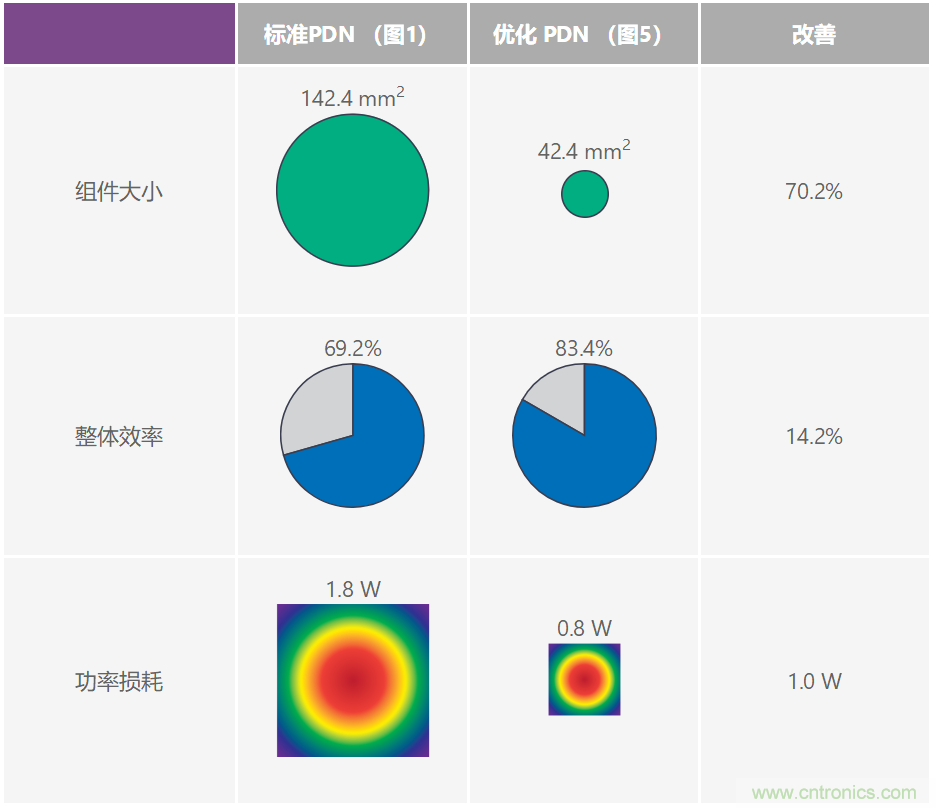

表1比較了優(yōu)化PDN和標準PDN(如圖1所示,由一個四通道降壓開關(guān)和三個LDO穩(wěn)壓器構(gòu)成)的性能�。從組件大小來看,優(yōu)化后的解決方案比標準解決方案減小70.2%�����。此外�,效率從69.2%提高到83.4%����,整體節(jié)能1.0 W。

表1.AD9175優(yōu)化PDN與標準PDN進行比較

圖5.AD9175高速DAC的優(yōu)化PDN���。

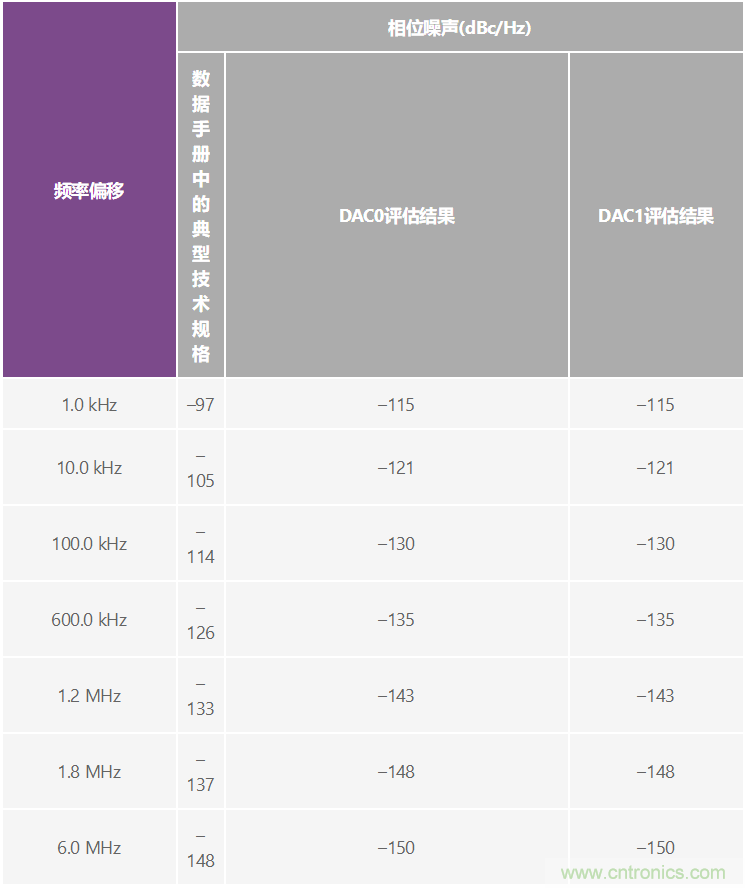

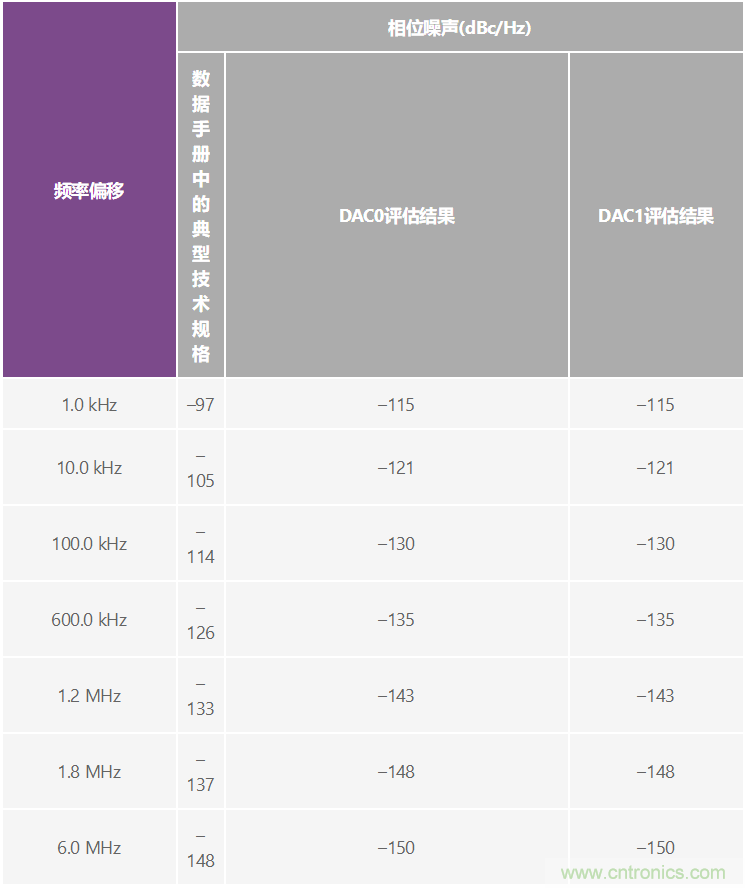

為了驗證優(yōu)化PDN的噪聲性能是否足以滿足高性能技術(shù)規(guī)格要求�,對AD9175進行相位噪聲評估����,并檢測載波周圍邊帶雜散的DAC輸出頻譜。1如表2所示����,相位噪聲檢測結(jié)果在數(shù)據(jù)手冊技術(shù)規(guī)格規(guī)定的限值內(nèi)����。AD9175輸出頻譜的載波頻率很干凈�,沒有可見的邊帶雜散,如圖6所示���。

圖6.使用優(yōu)化PDN的AD9175輸出頻譜(1.8 GHz����、–7 dBFS載波)����。

表2.使用圖5中的優(yōu)化PDN時,AD9175在1.8 GHz載波下的相位噪聲

AD9213 10.25 GSPS高速模數(shù)轉(zhuǎn)換器的電源系統(tǒng)優(yōu)化

AD9213是一款單通道��、12位、6 GSPS或10.25 GSPS���、射頻(RF)模數(shù)轉(zhuǎn)換器(ADC),具有6.5 GHz輸入帶寬。AD9213支持高動態(tài)范圍頻率和需要寬瞬時帶寬和低轉(zhuǎn)換誤差率(CER)的時域應(yīng)用��。AD9213具有16通道JESD204B接口,以支持最大帶寬能力���。

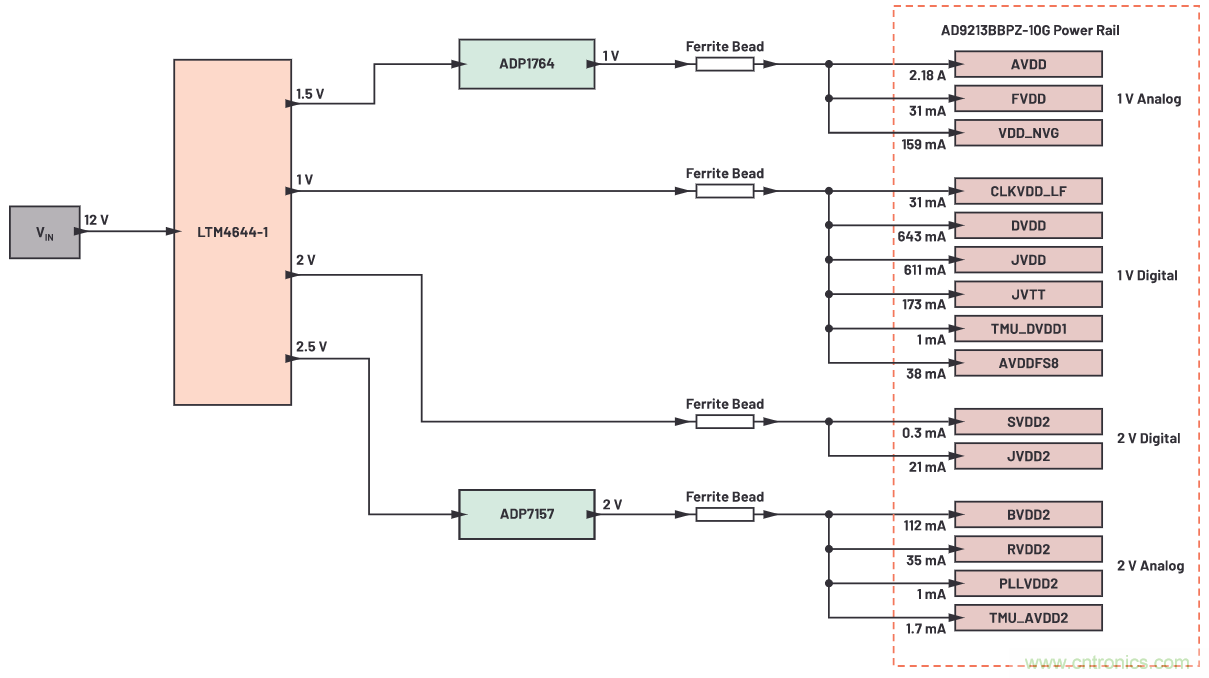

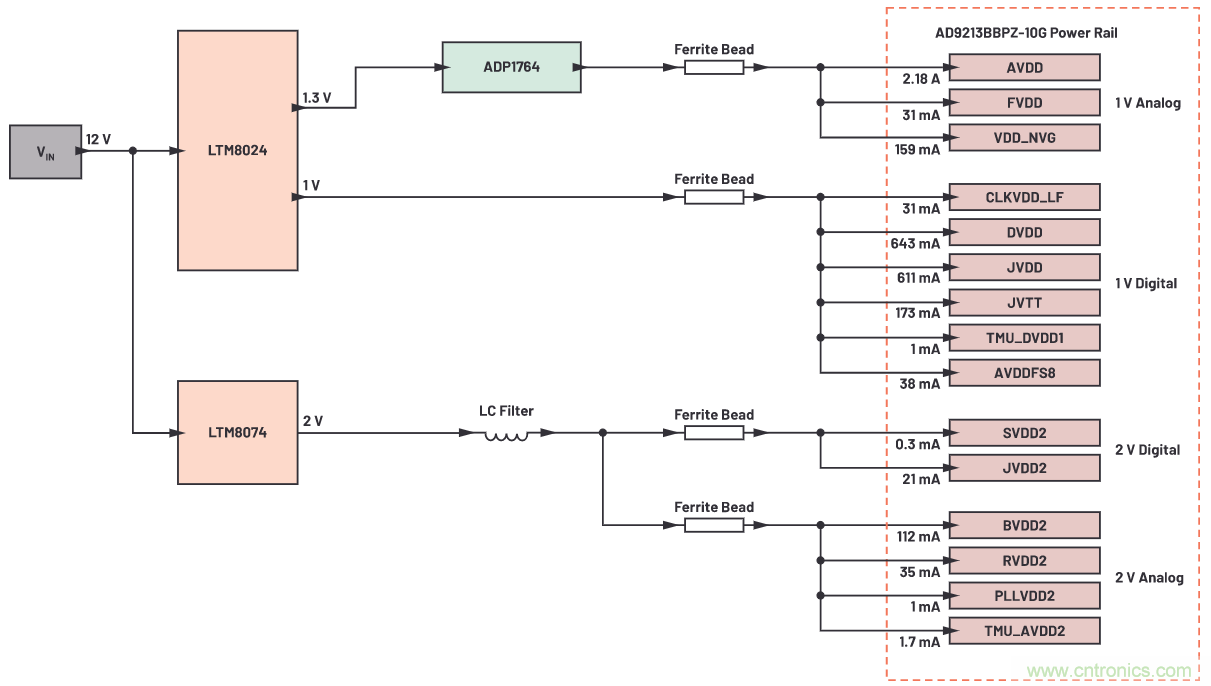

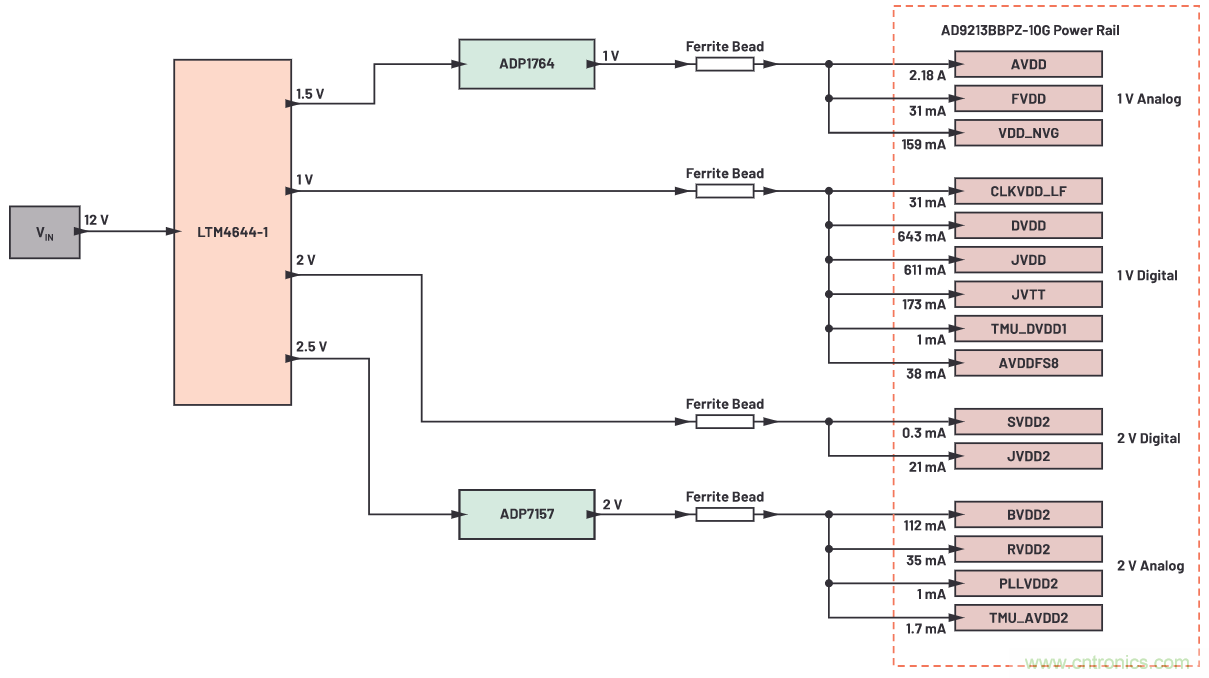

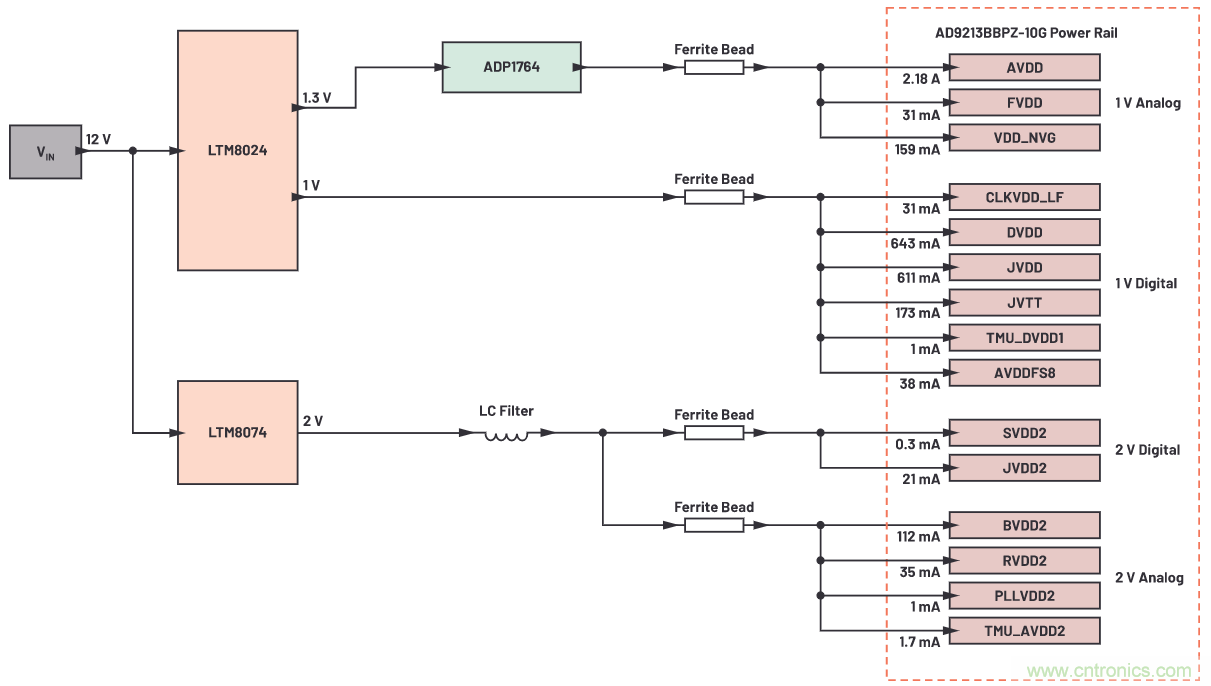

圖7顯示現(xiàn)成評估板上AD9213高速ADC的標準配電網(wǎng)絡(luò),由一個 LTM4644-1 µModule® 四通道開關(guān)和兩個線性穩(wěn)壓器構(gòu)成���。 該解決方案的大小和能效都較為高效,但它還可以改進嗎��?如本系列文章所述,優(yōu)化的第一步是量化AD9213的靈敏度——即實際設(shè)置PDN輸出噪聲的限值�,以免導(dǎo)致ADC性能大幅下降�。在這里���,我們將介紹使用兩個µModule穩(wěn)壓器的另一種替代PDN解決方案,并比較該方案與標準現(xiàn)成解決方案的性能�。

AD9213 10 GSPS ADC需要15個不同的電源軌,這些電源軌可以分為4組:

● 1 V模擬(3個電源軌)

● 1 V數(shù)字(6個電源軌)

● 2 V模擬(2個電源軌)

● 2 V數(shù)字(4個電源軌)

圖7.集成在現(xiàn)成評估板上的AD9213高速DAC的標準PDN���。

分析:噪聲要求

我們探討的優(yōu)化解決方案使用兩個µModule穩(wěn)壓器(LTM8024和LTM8074)和一個LDO后置穩(wěn)壓器取代LTM4644-1 µModule四通道開關(guān)和兩個線性穩(wěn)壓器���。

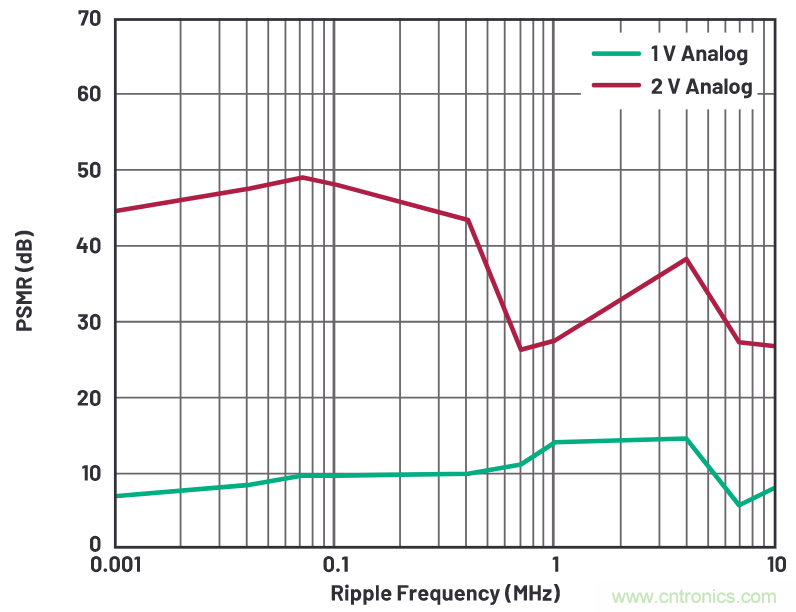

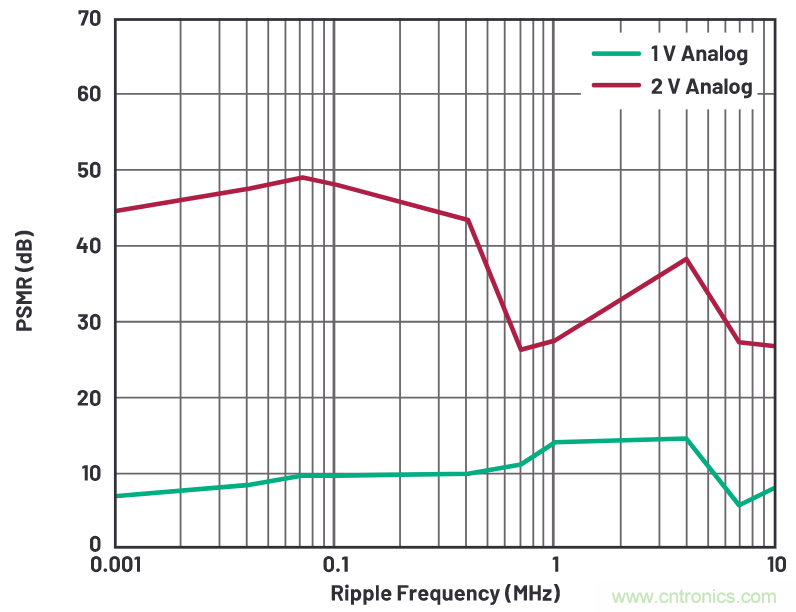

圖8.在2.6 GHz載波頻率下�����,AD9213高速ADC的1 V模擬電源軌和2 V模擬電源軌的PSMR���。

圖8顯示在2.6 GHz載波頻率下,AD9213的1 V模擬電源軌和2 V模擬電源軌的PSMR結(jié)果�。1 V模擬電源軌的PSMR比2 V模擬電源軌更低��,所以它更加敏感�。

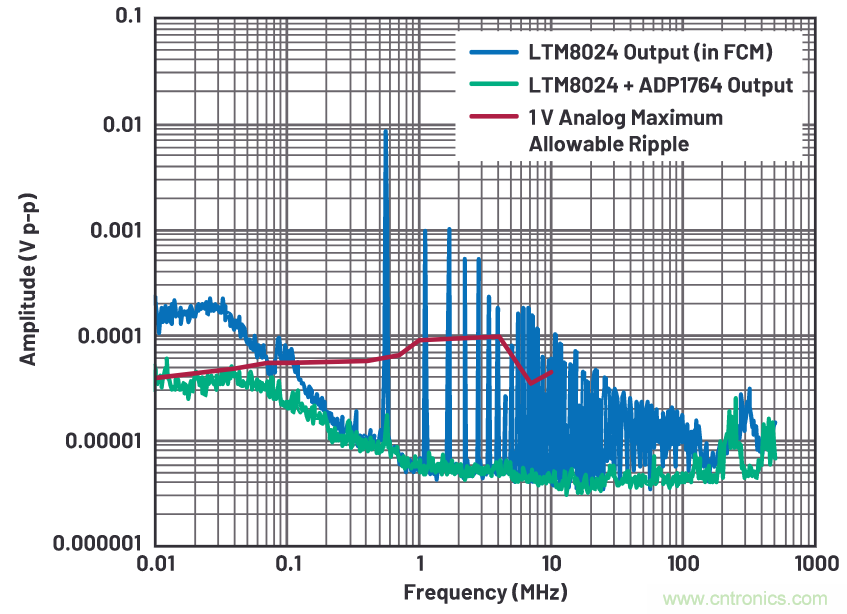

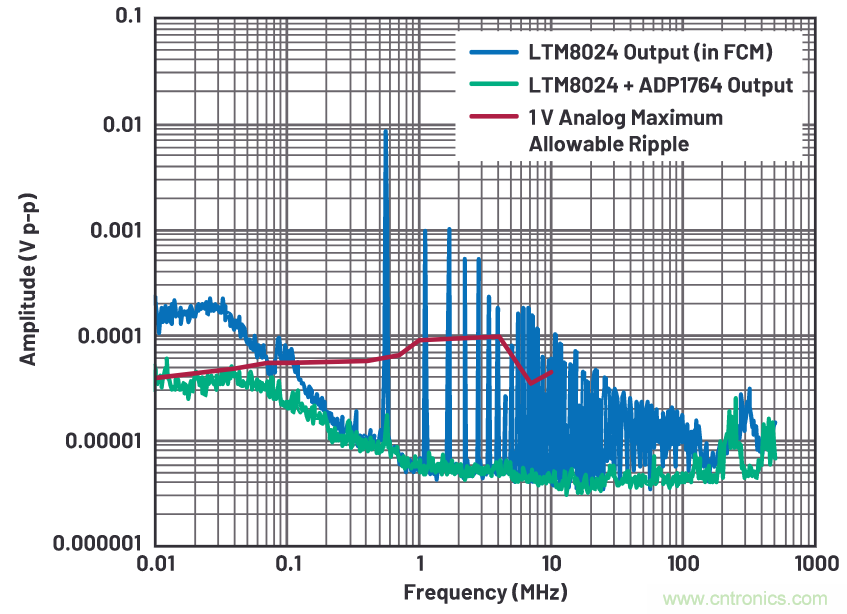

圖9顯示LTM8024(帶和不帶LDO穩(wěn)壓器)在強制連續(xù)模式(FCM)下的頻譜輸出����。圖中還顯示最大允許電壓紋波閾值的疊加不會在AD9213輸出頻譜的–98 dBFS本底噪聲中產(chǎn)生雜散����。直接為1 V模擬電源軌供電時���,LTM8024輸出中未經(jīng)濾波的1/f噪聲和基波開關(guān)雜散超過了最大允許紋波閾值。

為LTM8024添加 ADP1764 LDO后置穩(wěn)壓器可將1/f噪聲�、基本開關(guān)紋波及其諧波降低至最大允許紋波閾值以下,如圖9所示�����。 需要在線性穩(wěn)壓器輸入端提供一些裕量電壓。在本例中�,從LTM8024輸出1.3 V至后置穩(wěn)壓器的輸入����。這個300 mV符合LDO穩(wěn)壓器的推薦裕量電壓規(guī)格����,同時能夠最大限度降低其功率損耗;比標準解決方案使用的500 mV更為合適����。

圖9.LTM8024頻譜輸出與1 V模擬電源軌的最大允許紋波閾值之間的關(guān)系����。

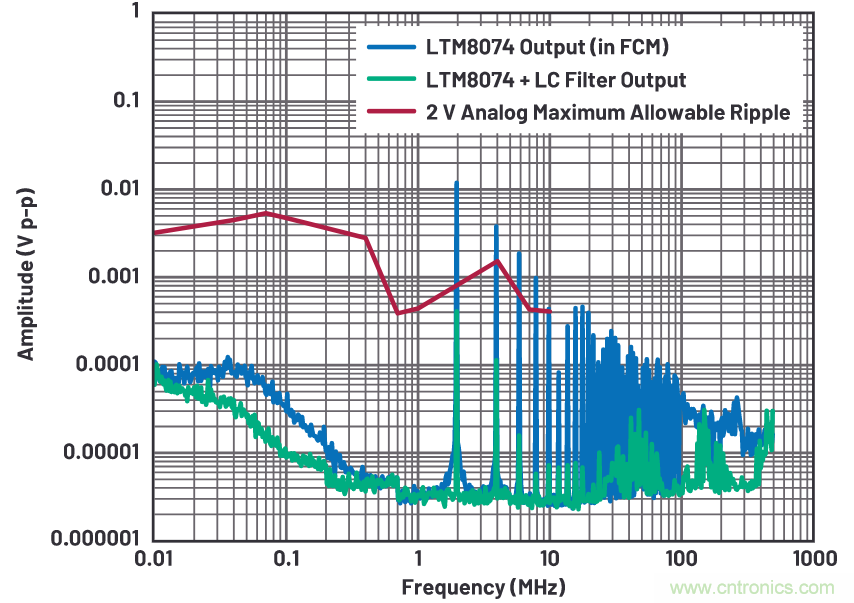

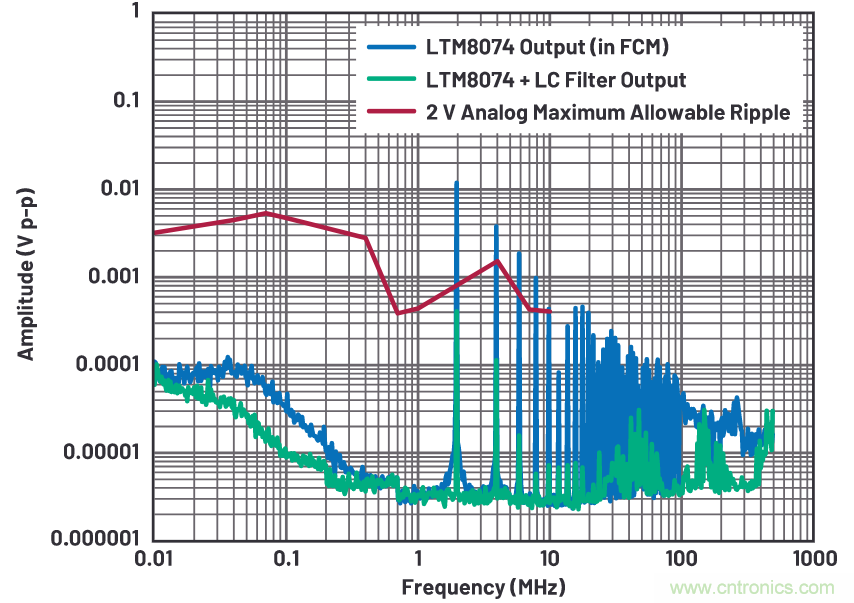

對于2 V電源軌:圖10顯示LTM8074 µModule穩(wěn)壓器(帶和不帶LC濾波器)在強制連續(xù)模式下的頻譜輸出���。圖中也顯示了最大允許電壓紋波閾值���。此閾值代表電源紋波電平,當(dāng)超過該值時���,DAC載波信號中的邊帶雜散將出現(xiàn)在AD9213輸出頻譜的–98 dBFS本底噪聲上方���。這里,與1 V模擬電源軌類似����,直接為2 V模擬電源軌供電時,穩(wěn)壓器開關(guān)雜散會超過最大允許紋波閾值�����。但是����,不需要LDO穩(wěn)壓器��,而是由LTM8074輸出端的LC濾波器將開關(guān)雜散降低至最大允許紋波閾值以下。

圖10.LTM8074頻譜輸出與2 V模擬電源軌的最大允許紋波閾值之間的關(guān)系�。

結(jié)果:優(yōu)化PDN

圖11顯示根據(jù)電源靈敏度評估結(jié)果得到的優(yōu)化配電網(wǎng)絡(luò)���。與標準解決方案一樣�����,它使用三個功率IC;在本例中���,分別是LTM8024���、LTM8074和ADP1764。在該解決方案中�,LTM8024 µModule穩(wěn)壓器VOUT1由ADP1764進行后置調(diào)節(jié)�,以便為相對敏感的1 V模擬電源軌供電。1 V數(shù)字電源軌直接由LTM8024的VOUT2供電����。與AD9175 DAC類似����,AD9213的數(shù)字電源軌對電源噪聲不太敏感,因此可以直接為這些電源軌供電��,并且不會降低DAC動態(tài)性能。帶有LC濾波器的LTM8074為2 V模擬和2 V數(shù)字電源軌供電���。

圖11.AD9213高速ADC的優(yōu)化PDN。

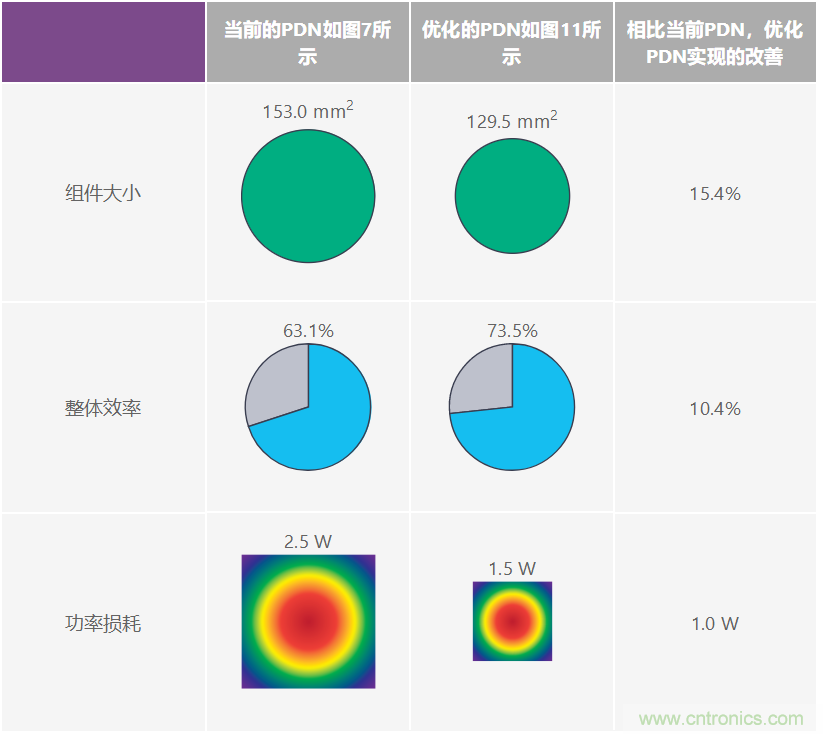

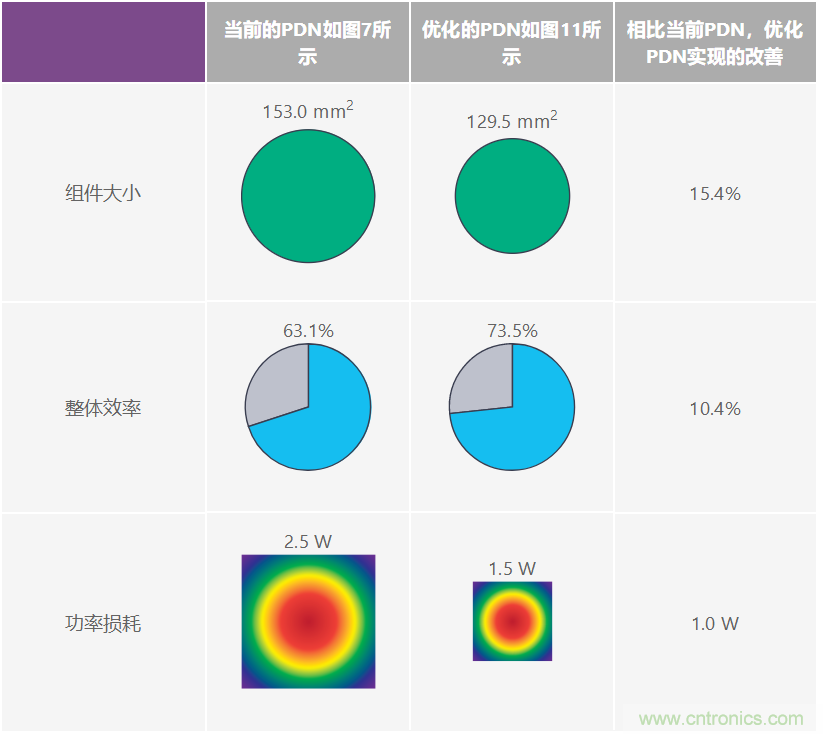

表3比較了優(yōu)化PDN與現(xiàn)成標準PDN的性能�。如圖7所示,標準PDN使用一個四通道降壓開關(guān)和兩個LDO穩(wěn)壓器����。組件大小減小15.4%�����,效率從63.1%提高到73.5%�����,整體節(jié)能1.0 W。

表3.AD9213高速ADC的優(yōu)化PDN與標準PDN比較

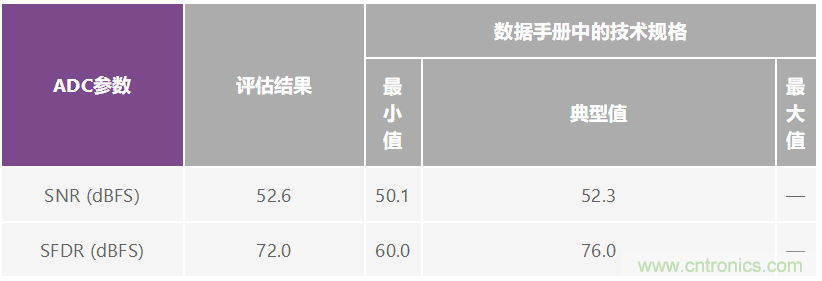

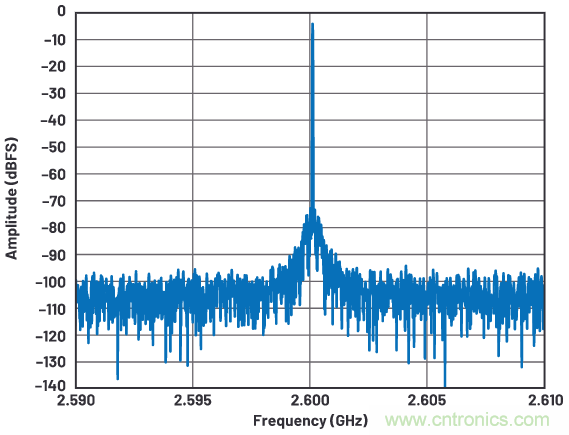

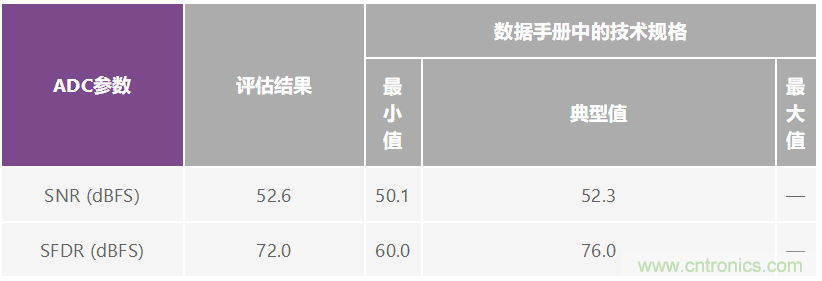

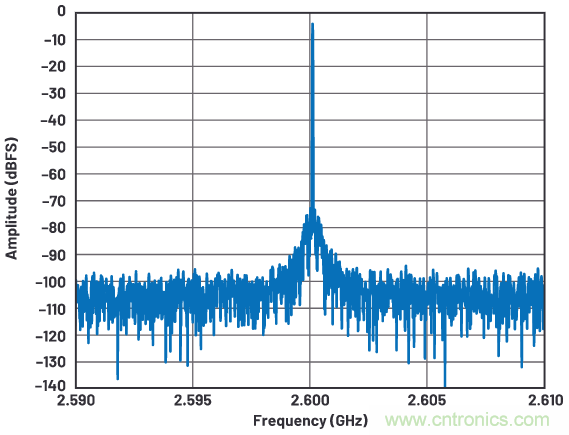

為了驗證優(yōu)化PDN的性能����,從SFDR和SNR兩個方面對AD9213進行評估����,并檢查載波周圍邊帶雜散的FFT輸出頻譜��。結(jié)果顯示��,SNR和SFDR的性能在數(shù)據(jù)手冊給出的技術(shù)規(guī)格限值范圍內(nèi),如表4所示�。圖12顯示AD9213的FFT輸出頻譜�,其載波頻率很干凈��,沒有可見的邊帶雜散���。

表4.使用圖11中的優(yōu)化PDN時�,AD9213在2.6 Ghz載波下的動態(tài)性能

圖12.使用圖11中的優(yōu)化PDN時�,AD9213的FFT頻譜(2.6 GHz��、–1 dBFS載波)��。

結(jié)論

高性能數(shù)據(jù)轉(zhuǎn)換器的現(xiàn)成評估板中包含配電網(wǎng)絡(luò),旨在滿足這些信號處理IC的噪聲要求����。即使這些評估板在設(shè)計時經(jīng)過了仔細考量,配電網(wǎng)絡(luò)仍有改進的空間���。本文研究了兩種PDN:一種適用于高速DAC,一種適用于高速ADC�。與標準PDN相比���,我們的優(yōu)化方案在空間要求、效率�,尤其是重要的熱性能方面都有所改進�。通過使用替代設(shè)計�,或當(dāng)前不可用的器件�����,可以進一步改善某些參數(shù)��。請繼續(xù)關(guān)注"電源系統(tǒng)優(yōu)化"系列文章����,包括RF收發(fā)器的PDN優(yōu)化���。

參考電路

1 Patrick Errgy Pasaquian and Pablo Perez, Jr�。"優(yōu)化信號鏈的電源系統(tǒng) — 第1部分: 多少電源噪聲可以接受���?" 模擬對話,第55卷第1期���,2021年3月。

Delos, Peter�。"電源調(diào)制比揭秘:PSMR與PSRR有何不同��?" ADI公司�,2018年12月���。

Delos���、Peter和Jarrett Liner����。"改進的DAC相位噪聲測量支持超低相位噪聲DDS應(yīng)用" 模擬對話�����,第51卷第3期��,2017年8月。

"數(shù)據(jù)轉(zhuǎn)換基本指南" ADI公司��。

Umesh Jayamohan����。 "為GSPS或RF采樣ADC供電:開關(guān)與LDO" ����,ADI公司����,2015年11月���。

Limjoco���、Aldrick�、Patrick Errgy Pasaquian和Jefferson Eco����。 "Silent Switcher µModule穩(wěn)壓器為GSPS采樣ADC提供低噪聲供電�,并節(jié)省一半空間" ADI公司,2018年10月���。

Eco, Jefferson和Aldrick Limjoco�。"鐵氧體磁珠揭秘" 模擬對話�,第50卷第1期��,2016年2月。

Umesh Jayamohan���。 "高速ADC電源域非常見問題解答" 模擬對話���,第52卷第2期��,2018年5月。

免責(zé)聲明:本文為轉(zhuǎn)載文章���,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有���。本文所用視頻��、圖片、文字如涉及作品版權(quán)問題��,請聯(lián)系小編進行處理����。

推薦閱讀: