【導(dǎo)讀】在測(cè)試測(cè)量相關(guān)應(yīng)用中,模擬開關(guān)和多路復(fù)用器有著非常廣泛的應(yīng)用,例如運(yùn)放的增益調(diào)節(jié)、ADC分時(shí)采集多路傳感器信號(hào)等等。雖然它的功能很簡(jiǎn)單,但是仍然有很多細(xì)節(jié),需要大家在使用的過程中注意。所以,在這里為大家介紹一下模擬開關(guān)和多路復(fù)用器的基礎(chǔ)參數(shù)。

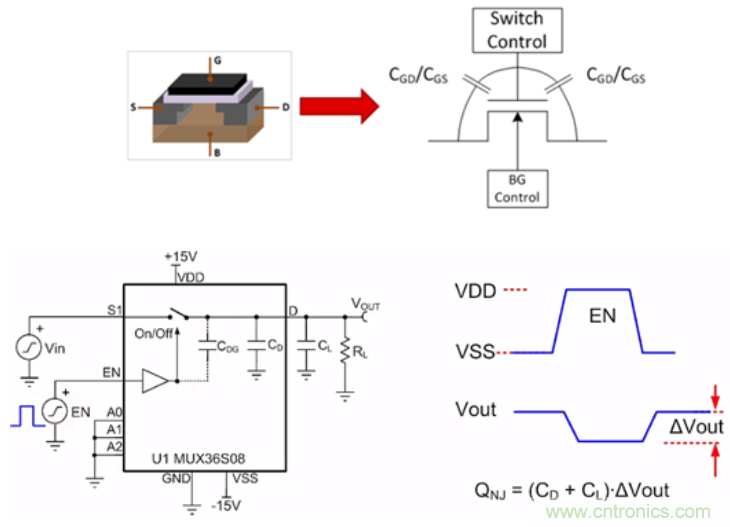

在開始介紹基礎(chǔ)的參數(shù)之前,我們有必要介紹一下模擬開關(guān)和多路復(fù)用器的基本單元MOSFET開關(guān)的基本結(jié)構(gòu)。

一. MOSFET開關(guān)的架構(gòu)

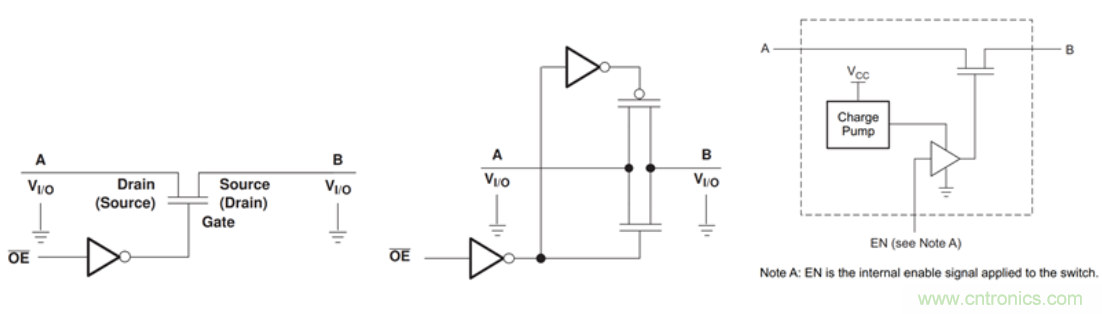

MOSFET開關(guān)常見的架構(gòu)有3種,如圖1所示。

1)NFET。

2)NFET和PFET。

3)帶有電荷泵的NFET。

三種架構(gòu)各有特點(diǎn),詳細(xì)的介紹,可以參考《TI Precision Labs - Switches and Multiplexers》培訓(xùn)視頻和《Selecting the Right Texas Instruments Signal Switch》應(yīng)用文檔。本文主要基于NFET和PFET架構(gòu)展開介紹和仿真,但是涉及到的概念在三種架構(gòu)中都是適用的。

圖 1 MOSFET開關(guān)結(jié)構(gòu)

另外,需要注意的是,此處的MOSFET結(jié)構(gòu),S和D是對(duì)稱的,所以在功能上是可以互換的,也因此,開關(guān)是雙向的,為了便于討論,我們統(tǒng)一把S極作為輸入。

二.模擬開關(guān)和多路復(fù)用器直流參數(shù)介紹

1. 導(dǎo)通電阻 On Resistance

(1). 定義

圖 2 On Resistance 定義

(2). 特點(diǎn)

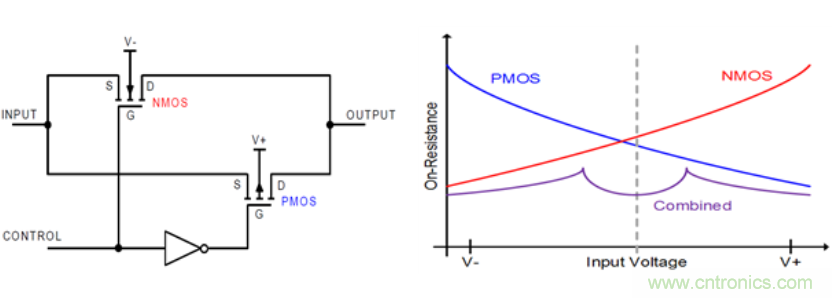

1) 隨輸入信號(hào)電壓而改變:當(dāng)芯片的供電電壓固定時(shí),對(duì)于NMOS而言,S級(jí)的電壓越高,導(dǎo)通電阻越來越大,對(duì)于PMOS而言,S級(jí)的電壓越高,導(dǎo)通電阻越來越小。

圖 3 導(dǎo)通電阻隨輸入信號(hào)電壓變化的曲線

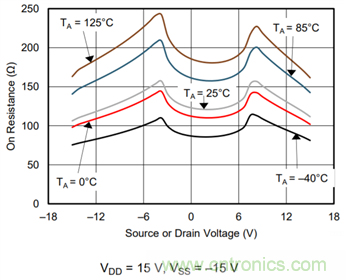

2) 導(dǎo)通電阻的阻值與溫度有關(guān):當(dāng)VDD和VSS固定不變時(shí),隨著溫度的升高,導(dǎo)通電阻的曲線整體向上平移。

圖 4 導(dǎo)通電阻隨溫度變化的曲線

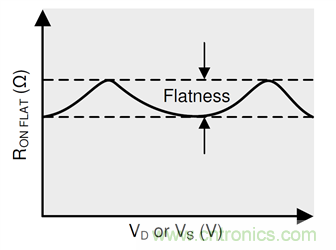

3) 導(dǎo)通電阻的平坦度:On-resistance flatness

圖 5 On-resistance flatness

在一定的輸入電壓范圍內(nèi),導(dǎo)通電阻的最大值與最小值的差稱為導(dǎo)通電阻的平坦度,這個(gè)值越大,說明導(dǎo)通電阻的變化幅度越大。

(3). 影響

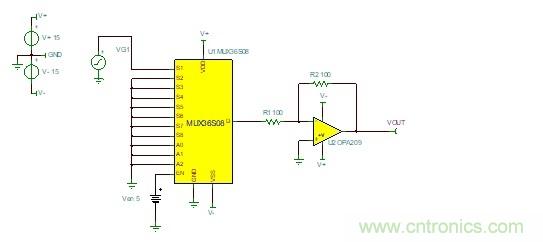

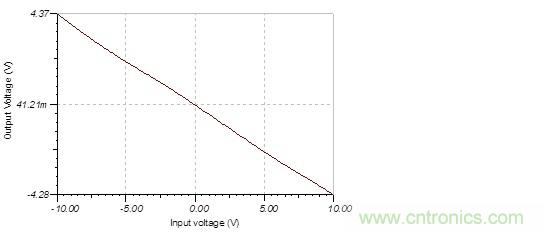

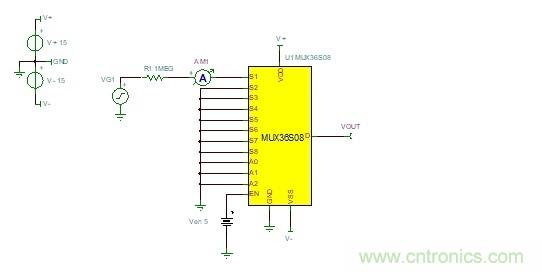

在這里,我們通過一個(gè)仿真實(shí)例來觀察一下導(dǎo)通電阻及平坦度對(duì)于系統(tǒng)的影響,如圖6。為了更容易地觀察到影響,我們選擇設(shè)置R1和R2為100?。

圖 6 MUX36S08仿真電路

圖 7 輸入及輸出波形

從仿真的結(jié)果我們可以看出:

1) 輸出電壓并不是我們輸入電壓乘以放大比例后的結(jié)果,這是因?yàn)橛袑?dǎo)通電阻的存在。

2) 輸出電壓隨輸入電壓的并不是線性關(guān)系,這是因?yàn)镽on隨著Vin在變化,會(huì)在輸出端引入非線性誤差。所以,Ron的平坦度越小,輸出的非線性誤差越小。

2.漏電流 Leakage current

(1). 定義

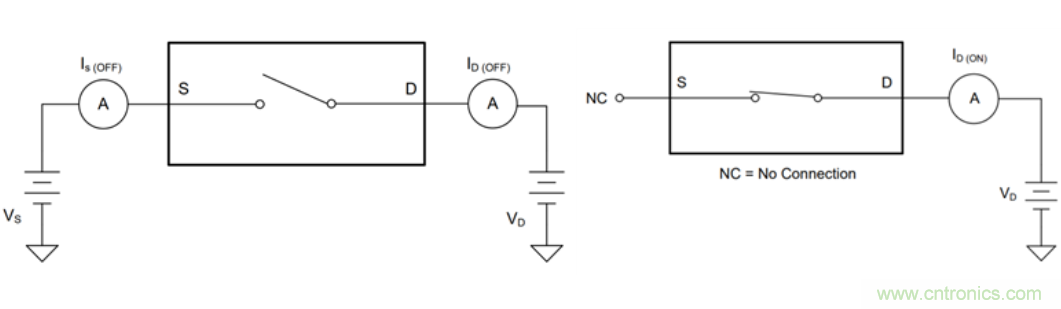

1) Source off-leakage current: 在開關(guān)斷開時(shí),從源極流入或流出的電流稱為 ,如圖8。

,如圖8。

2) Drain off-leakage current: 在開關(guān)斷開時(shí),從漏極流入或流出的電流稱為 ,如圖8

,如圖8

3) On-leakage current: 當(dāng)開關(guān)閉合時(shí),從漏極流入或流出的電流稱為 ,如圖8。

,如圖8。

圖 8 漏電流定義

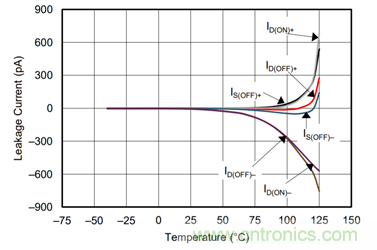

(2). 特點(diǎn)

漏電流隨溫度變化劇烈。

圖 9 漏電流隨溫度變化的曲線

(3). 影響

在很多數(shù)據(jù)采集系統(tǒng)中,接入MUX前的傳感器有可能是高阻抗的傳感器。這時(shí),漏電流的影響就會(huì)凸顯出來。

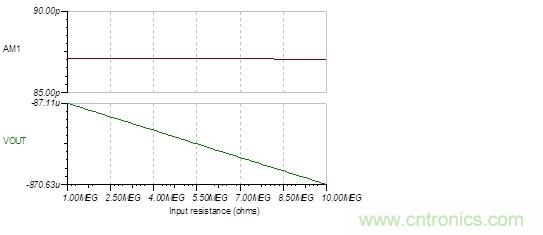

例如,在圖10的仿真中,輸入源有1M?的源阻抗,我們對(duì)這個(gè)電阻進(jìn)行直流參數(shù)掃描,觀察它從1M?變化至10M?時(shí),對(duì)輸出電壓的影響,結(jié)果可以看到,漏電流通過傳感器的內(nèi)阻會(huì)給輸出電壓帶來一個(gè)直流誤差。所以,在為高輸出阻抗的傳感器選擇MUX時(shí),要盡可能選取低漏電流的芯片。

圖 10 漏電流仿真電路

圖 11 漏電流仿真結(jié)果

三. 模擬開關(guān)和多路復(fù)用器動(dòng)態(tài)參數(shù)介紹

1. 導(dǎo)通電容 On Capacitance

(1). 定義

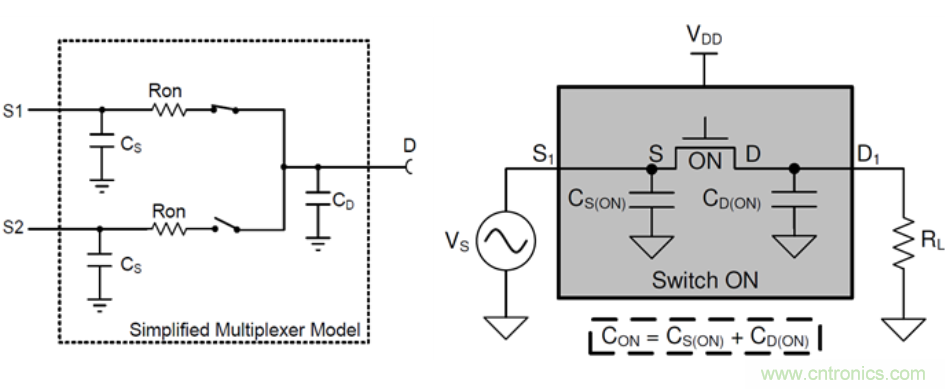

CS和CD代表了開關(guān)在斷開時(shí)的源極和漏極電容。當(dāng)開關(guān)導(dǎo)通時(shí),CON等于源極的電容和漏極的電容之和,如圖12。

圖 12 On Capacitance

(2). 影響

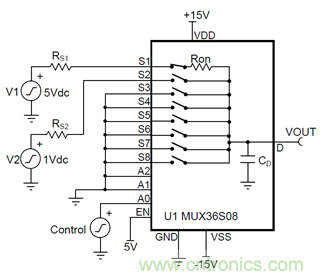

圖 13 MUX36S08 示例

當(dāng)MUX在不同通道之間切換時(shí),CD也會(huì)隨著通道的切換被充電或者放電。例如,當(dāng)S1閉合時(shí),CD會(huì)被充電至V1。那么此時(shí)CD上的電荷QD1:

當(dāng)MUX從S1切換至S2時(shí),CD會(huì)被充電至V2。那么此時(shí)CD上的電荷QD2:

那么兩次CD上的電荷差就需要V2來提供,所以這時(shí)候,MUX輸出就會(huì)需要一定的時(shí)間來穩(wěn)定。

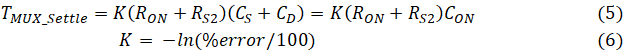

對(duì)于一個(gè)N-bit的ADC:

K其實(shí)是代表RC電路中,電壓到達(dá)目標(biāo)誤差以內(nèi)時(shí)所需要的時(shí)間常數(shù)的數(shù)量,例如10-bit accuracy (LSB % FS= 0.0977), K= -ln (0.0977/100)=6.931。

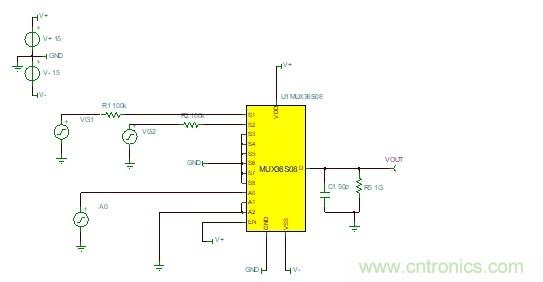

接下來用一個(gè)仿真來說明這種現(xiàn)象:

為了更明顯地觀察到這種現(xiàn)象,在Vout 端加入一個(gè)電容C1,可以理解為增加了CD,也可以理解為負(fù)載電容和CD的并聯(lián)。

圖 14 On Capacitance對(duì)輸出影響的仿真示例電路

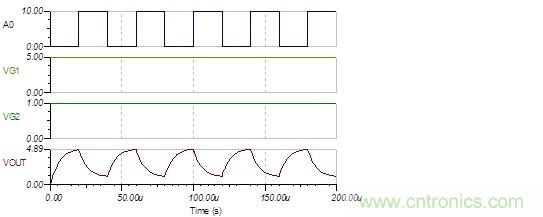

當(dāng) 時(shí),整個(gè)回路的時(shí)間常數(shù)較大,需要更長時(shí)間穩(wěn)定,所以在開關(guān)導(dǎo)通20uS之后,輸出電壓仍然沒有穩(wěn)定到信號(hào)源的電壓。

時(shí),整個(gè)回路的時(shí)間常數(shù)較大,需要更長時(shí)間穩(wěn)定,所以在開關(guān)導(dǎo)通20uS之后,輸出電壓仍然沒有穩(wěn)定到信號(hào)源的電壓。

圖 15 C1=50pF 仿真結(jié)果

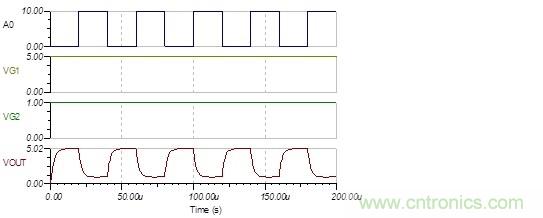

當(dāng) 時(shí),整個(gè)回路的時(shí)間常數(shù)較小,需要較短時(shí)間穩(wěn)定,所以在開關(guān)導(dǎo)通20uS之內(nèi),輸出電壓穩(wěn)定到了信號(hào)源的電壓。

時(shí),整個(gè)回路的時(shí)間常數(shù)較小,需要較短時(shí)間穩(wěn)定,所以在開關(guān)導(dǎo)通20uS之內(nèi),輸出電壓穩(wěn)定到了信號(hào)源的電壓。

圖 16 C1=10pF 仿真結(jié)果

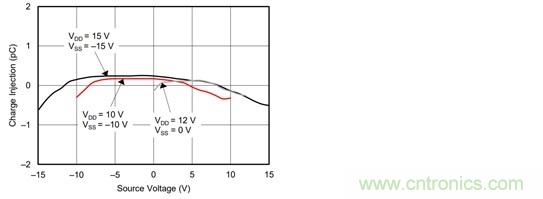

2. 注入電荷 Charge Injection

(1). 定義

注入電荷指的是從控制端EN耦合至輸出端的電荷。

(2). 影響

因?yàn)樵陂_關(guān)導(dǎo)通的通道上,缺乏消耗這部分電荷的通路,所以當(dāng)這部分電荷流入漏極電容和輸出電容上時(shí),會(huì)在輸出產(chǎn)生一個(gè)電壓誤差。

圖 17 Charge Injection過程示意圖

過程如下:

當(dāng)在EN端有一個(gè)階躍信號(hào)時(shí),這個(gè)階躍電壓會(huì)通過柵極和漏極之間的寄生電容CGD,耦合至輸出端,輸出電壓的改變?nèi)Q于注入電荷QINJ,CD和CL。

所以,當(dāng)注入的電荷越小時(shí),在輸出端引入的誤差會(huì)越小。

但同時(shí),要注意到,注入電荷是一個(gè)與供電電壓、輸入信號(hào)都有關(guān)的一個(gè)參數(shù)。因此,當(dāng)輸入信號(hào)的電壓在變化時(shí),會(huì)在輸出端產(chǎn)生一個(gè)非線性的誤差。所以在選在MUX時(shí),除了要注意charge injection的值以外,也要注意charge injection在輸入范圍內(nèi)的平坦度。

圖 18 MUX36S08 charge injection 曲線

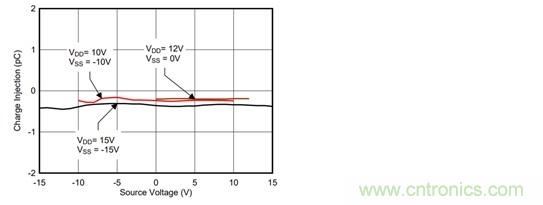

TMUX6104精密模擬多路復(fù)用器使用特殊的電荷注入消除電路,可將源極-漏極電荷注入在VSS = 0 V時(shí)降至-0.35 pC,在整個(gè)信號(hào)范圍內(nèi)降至-0.41 pC。

圖 19 TMUX6104 Charge Injection 曲線

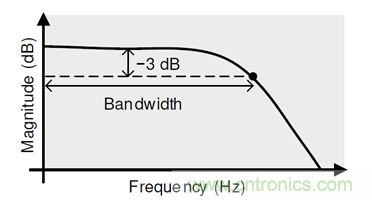

3. 帶寬Bandwidth

(1). 定義

當(dāng)開關(guān)打開時(shí),在漏極的輸出刪減至源極輸入衰減3dB時(shí)的頻率,如圖20所示。

圖 20 帶寬定義

(2). 計(jì)算方法

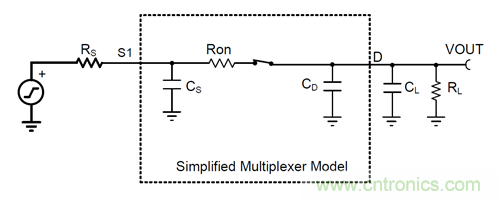

圖 21 簡(jiǎn)化的MUX內(nèi)部的開關(guān)模型

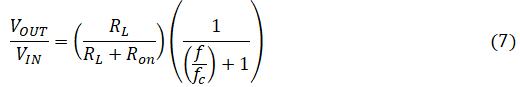

為了簡(jiǎn)化分析,我們忽略RS和CS。根據(jù)圖21中的阻容網(wǎng)絡(luò),我們可以寫出該電路的傳遞函數(shù):

其中,3dB cut off frequency:

根據(jù)這個(gè)公式,結(jié)合MUX和負(fù)載的參數(shù),我們就可以算出來在當(dāng)前條件下MUX的帶寬了。

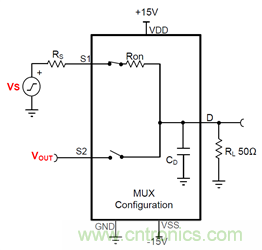

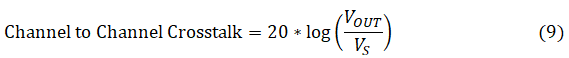

4. 通道間串?dāng)_ Channel to Channel crosstalk

(1). 定義

圖 22 通道間串?dāng)_示意圖

通道間串?dāng)_定義為當(dāng)已知信號(hào)施加到導(dǎo)通通道的源極引腳時(shí),在截止通道的源極引腳上出現(xiàn)的電壓。

(2). 特點(diǎn)

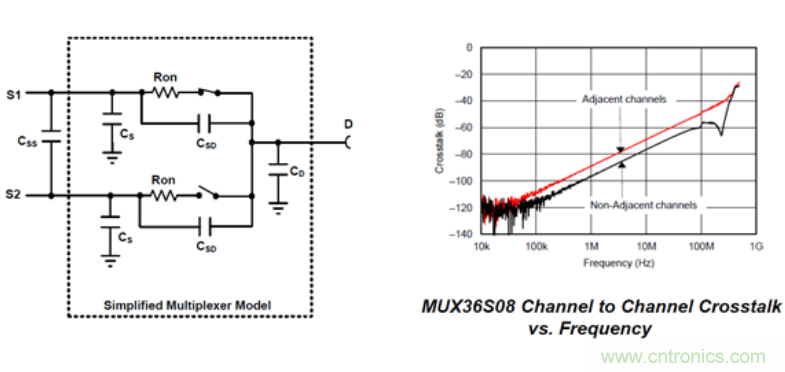

圖 23 簡(jiǎn)化的MUX內(nèi)部的開關(guān)模型及通道間串?dāng)_隨信號(hào)頻率的變化

Channel to Channel crosstalk是和頻率有關(guān)的一種現(xiàn)象。主要是由于關(guān)斷狀態(tài)下寄生電容導(dǎo)致的。有時(shí),也會(huì)由于布局技術(shù)不佳而引入了寄生電容,表現(xiàn)為串?dāng)_。

CSS表示兩個(gè)輸入通道之間的寄生電容。 這可能是傳輸信號(hào)的兩個(gè)輸入走線之間的電容,或者是多路復(fù)用器的兩個(gè)輸入引腳之間的電容。

在較低頻率的時(shí)候,從S1到OUTPUT的阻抗是RON ,因?yàn)镾2是斷開的,從S2到OUTPUT的阻抗非常高。隨著施加到S1的輸入信號(hào)的頻率增加,寄生電容CSD的阻抗變得更低,并在S2引入了一部分S1的輸入信號(hào)。

相同的原理,寄生電容CSS隨頻率的增加也會(huì)將一部分輸入信號(hào)直接耦合到斷開的通道S2。

減少雜散電容的電路板布局技術(shù)也會(huì)有助于通道間的串?dāng)_問題。

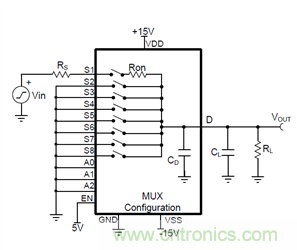

5. 關(guān)斷隔離 Off isolation

(1). 定義

關(guān)斷隔離定義為當(dāng)在關(guān)閉通道的源極引腳上施加已知信號(hào)時(shí)在多路復(fù)用器輸出引腳上引入的電壓。

圖 24 關(guān)斷隔離示意圖

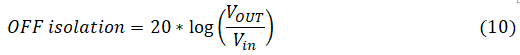

(2). 特點(diǎn)

圖 25 簡(jiǎn)化的MUX內(nèi)部的開關(guān)模型及關(guān)斷隔離隨信號(hào)頻率的變化

像串?dāng)_一樣,關(guān)斷隔離也是一種與頻率相關(guān)的現(xiàn)象,由于模擬開關(guān)或多路復(fù)用器的OFF狀態(tài)寄生電容CSD而發(fā)生。而開關(guān)在截止?fàn)顟B(tài)的寄生電容又取決于多個(gè)因素,例如器件封裝、引出線、制造工藝以及電路板布局技術(shù)。

較低的負(fù)載電阻將產(chǎn)生更好的OFF隔離,但由于導(dǎo)通電阻的存在,如果負(fù)載電阻過低,會(huì)引入失真。 較大的負(fù)載電容和漏極電容也將有助于更好的OFF隔離,但會(huì)限制多路復(fù)用器的帶寬。

關(guān)斷隔離和串?dāng)_規(guī)范都會(huì)分為相鄰和不相鄰?fù)ǖ纼深悺?/div>

推薦閱讀: