【導讀】高分辨率、逐次逼近型ADC的整體精度取決于精度、穩(wěn)定性和其基準電壓源的驅(qū)動能力。ADC基準電壓輸入端的開關(guān)電容具有動態(tài)負載,因此基準電壓源電路必須能夠處理與時間和吞吐速率相關(guān)的電流。某些ADC片上集成基準電壓源和基準電壓源緩沖器,但這類器件在功耗或性能方面可能并非最佳——通常使用外部基準電壓源電路才可達到最佳性能。本文探討基準電壓源電路設計中遇到的挑戰(zhàn)和要求。

基準電壓輸入

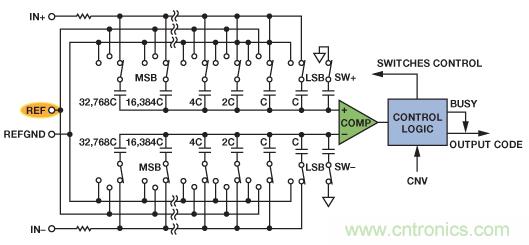

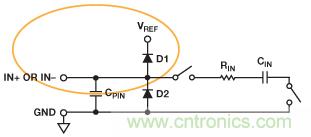

逐次逼近型ADC的簡化原理圖見圖1。采樣間隔期間,容性DAC連接至ADC輸入,并且與輸入電壓成比例的電荷被存儲在電容器中。轉(zhuǎn)換開始后,DAC從輸入端斷開。轉(zhuǎn)換算法逐個開關(guān)每一位至基準電壓或地。電容上的電荷再分配可導致電流流入或流出基準電壓源。動態(tài)電流負載是ADC吞吐速率和控制位檢驗的內(nèi)部時鐘的函數(shù)。最高有效位(MSB)保持大部分的電荷,需要大部分電流。

圖1. 16位逐次接近型ADC原理簡化圖

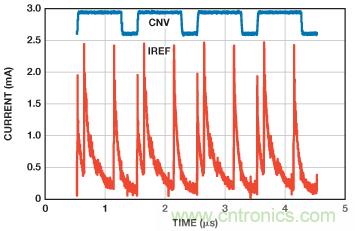

圖2顯示AD7980、16位、1 MSPS、PulSAR®逐次逼近型ADC基準電壓輸入端的動態(tài)電流負載。通過觀察基準電壓源和基準電壓引腳之間500 Ω電阻上的電壓降,得出測量值。曲線顯示電流尖峰高達2.5 mA,并且在整個轉(zhuǎn)換期間分布著較小的尖峰。

圖2. AD7980動態(tài)基準電流

若要支持該電流,同時保持基準電壓的無噪聲特性,需在盡可能靠近基準電壓輸入放置一個高數(shù)值、低ESR的儲能電容,通常為10 µF或更大。較大的電容會進一步平滑電流負載,并降低基準電壓源電路的負擔,但極大的電容會產(chǎn)生穩(wěn)定性問題?;鶞孰妷涸幢仨氁芴峁┕酀M基準電容所需的平均電流,而不會導致基準電壓下降過大。在ADC數(shù)據(jù)手冊中,基準輸入電流平均值通常在特定的吞吐速率下指定。例如,在AD7980數(shù)據(jù)手冊中,將1 MSPS下5 V基準電壓源的平均基準電流指定為330 µA典型值。兩次轉(zhuǎn)換之間不消耗電流,因此基準電流隨吞吐速率成線性變化,在100 kSPS時降至33 µA?;鶞孰妷涸?mdash;—或基準電壓緩沖器——在最高的目標頻率下必須具有足夠低的輸出阻抗,以便在ADC輸入端保持電壓水平,使電壓不至于因為電流而產(chǎn)生太大的壓降。

基準電壓源輸出驅(qū)動

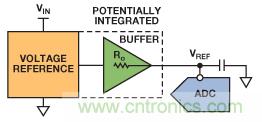

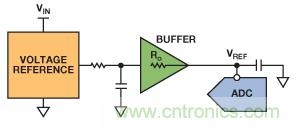

圖3顯示典型的基準電壓源電路?;鶞孰妷涸纯杉删哂凶銐蝌?qū)動電流的緩沖器,也可采用適當?shù)倪\算放大器作為緩沖器。為避免轉(zhuǎn)換誤差,特定吞吐速率下所需的平均電流不應使基準電壓下降超過½ LSB。該誤差在突發(fā)轉(zhuǎn)換中最為明顯,因為此吞吐速率下基準負載將從零變化到平均基準電流。

圖3. 典型精密逐次逼近型ADC基準電壓源電路

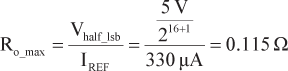

AD7980為16位ADC,其IREF = 330 µA , VREF = 5 V;使用該ADC作為確定基準電壓源是否具有足夠驅(qū)動能力的示例,則對于½ LSB壓降,最大允許輸出阻抗為:

大部分基準電壓源不指定輸出阻抗,但會指定負載調(diào)整率,通常以ppm/mA表示。將其乘以基準電壓并除以1000即可轉(zhuǎn)換為輸出阻抗。例如,"ADR435 超低噪聲XFET® 5-V 5 V基準電壓源指定流出電流時的最大負載調(diào)整率為15 ppm/mA。轉(zhuǎn)換為電阻,可得:

因此,就輸出阻抗而言,ADR435應該足夠了。它可流出的最大電流為10 mA,足夠處理330 µA的平均基準電流。當ADC輸入電壓超出基準電壓,哪怕只有很短的一段時間,它也會向基準電壓源注入電流,因此基準電壓源必須要能吸取一定量的電流。圖4顯示ADC和基準電壓輸入之間的二極管連接,在輸入超量程條件下它可造成電流流入基準電壓源。與某些老的基準電壓源不同,ADR435能吸收10 mA電流。

圖4. AD7980模擬輸入結(jié)構(gòu)

由于基準電流的參數(shù)要求與吞吐速率成線性關(guān)系,較低的吞吐速率或使用較低吞吐率的ADC(如500 kSPSAD7988-5 或100 kSPSAD7988-1 (IREF = 250 µA)時,可采用較高輸出阻抗(功耗較低)的基準電壓源。通過降低基準電流,可算出最大輸出阻抗。請注意,這些公式僅作參考準則,對選擇的基準電壓源必須測試硬件驅(qū)動能力。

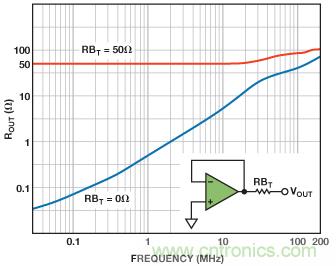

當所選基準電壓源的驅(qū)動能力不夠時,或者首選微功耗基準電壓源時,可使用基準電壓緩沖器??赏ㄟ^將適當?shù)倪\算放大器配置為單位增益而實現(xiàn)。運算放大器必須具有低噪聲和適當?shù)妮敵鲵?qū)動能力,并且要能夠穩(wěn)定工作在較大容性負載下。它還必須要能提供所需電流。通常不指定運算放大器的輸出阻抗,但一般可通過輸出阻抗與頻率的關(guān)系圖確定,如圖5中的AD803180 MHz軌到軌運算放大器所示。

圖5. AD8031ROUT 與頻率

位于100 kHz以下,則輸出阻抗低于0.1 Ω;而直流時則低于0.05 Ω,因此就我們1 MSPS下驅(qū)動AD7980的示例而言,它是不錯的選擇。在寬頻率范圍內(nèi)保持低輸出阻抗對于驅(qū)動基準電壓輸入而言非常重要。即便是較大的電容值,儲能電容也永遠無法消除基準電壓輸入端消耗的電流。電流紋波的頻率成分是吞吐速率和輸入信號帶寬的函數(shù)。大儲能電容處理與吞吐速率相關(guān)的高頻電流,而基準電壓緩沖器必須能夠在最大輸入信號頻率(或儲能電容阻抗變得足夠低,可提供所需電流的頻率)保持低阻抗?;鶞孰妷涸磾?shù)據(jù)手冊中的典型曲線顯示輸出阻抗與頻率的關(guān)系,選擇基準電壓源時應加以考慮。

AD8031就是一個很好的選擇,它在容性負載大于10 µF時性能穩(wěn)定。其它運算放大器(比如ADA4841也會在大電容下穩(wěn)定,因為它們主要驅(qū)動穩(wěn)定的直流電平,但某些特定的運算放大器必須測試確定加載特性。在電容之前使用串聯(lián)電阻以保持穩(wěn)定并不是個好主意,因為這會增加輸出阻抗。

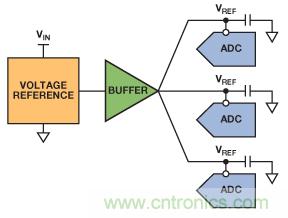

以一個基準電壓源驅(qū)動多個ADC時,基準電壓緩沖器非常有用,比如圖6中顯示的同步采樣應用中的情形。

圖6. 基準電壓源電路驅(qū)動多個ADC

所有ADC基準電壓輸入都有各自的儲能電容,盡可能靠近基準電壓輸入引腳放置。每條從基準電壓輸入出發(fā)的走線經(jīng)路由后返回位于基準電壓緩沖器輸出端的星型連接,最大程度降低串擾效應。具有低輸出阻抗和高輸出電流能力的基準電壓緩沖器可驅(qū)動許多ADC,具體取決于電流要求。請注意,緩沖器必須要能在額外電容下穩(wěn)定,該額外電容與多個基準電壓電容有關(guān)。

噪聲和溫度漂移

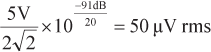

一旦確定了驅(qū)動能力,必須確?;鶞孰妷涸措娐返脑肼暡挥绊慉DC性能。為了保持信噪比(SNR)和其它規(guī)格,必須將基準電壓源噪聲貢獻限定為ADC噪聲的一小部分(比較理想的是20%或更低)。AD7980集成5 V基準電壓源,額定SNR為91 dB。轉(zhuǎn)換為rms可得:

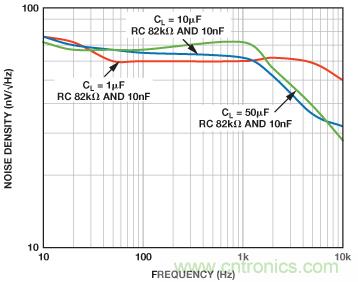

因此,基準電壓源電路應具有不超過10 µV rms的噪聲,以便最大程度減少對SNR造成的影響?;鶞孰妷涸春瓦\算放大器的噪聲規(guī)格通常可分為兩部分:低頻噪聲(1/f)和寬帶噪聲。結(jié)合這兩部分可得到基準電壓源電路的總噪聲貢獻。圖7顯示ADR4312.5 V基準電壓源的典型噪聲與頻率關(guān)系曲線圖。

圖7. 帶補償網(wǎng)絡的ADR431噪聲曲線

ADR435補償其內(nèi)部運算放大器,驅(qū)動大容性負載并避免噪聲峰化,使其非常適合與ADC一同使用。更詳盡的敘述可參見數(shù)據(jù)手冊。采用10 µF電容,其噪聲額定值為8 µV p-p 1/f(0.1 Hz至10 Hz),寬帶噪聲頻譜密度為115 nV/√Hz。估計噪聲帶寬為3 kHz。若要將1/f噪聲從峰峰值轉(zhuǎn)換為均方根(rms),可除以6.6:

然后,使用10 µF電容下的估計帶寬計算寬帶噪聲貢獻。有效帶寬由下式確定:

使用該有效帶寬計算rms寬帶噪聲:

總rms噪聲是低頻噪聲和寬帶噪聲的平方和開根:

結(jié)果低于10 µV rms,因此不會對ADC的SNR造成太大影響。這些計算可用來估算基準電壓源的噪聲貢獻,以判斷其穩(wěn)定性,但需要在工作臺上使用真實硬件對數(shù)據(jù)進行驗證。

若緩沖器在基準電壓源之后使用,則同樣的分析可用于計算噪聲貢獻。例如,AD8031具有15 nV/√Hz的噪聲頻譜密度。由于輸出端具有10 µF電容,其測量帶寬下降至大約16 kHz。使用此帶寬和噪聲密度,同時忽略1/f噪聲,則噪聲貢獻為2.4 µV rms。對基準電壓源緩沖器噪聲和基準電壓源噪聲進行平方和開根計算,即可得到總噪聲的估算值。通常,基準電壓源緩沖器的噪聲密度遠低于基準電壓源噪聲密度。

使用基準電壓源緩沖器時,可通過在基準電壓輸出添加一個極低截止頻率的RC濾波器,對來自基準電壓源的噪聲進行帶寬限制,如圖8所示。考慮到基準電壓源通常是噪聲的主要來源,這樣做可能會非常有效。

圖8. 帶RC濾波的基準電壓源

選擇基準電壓源時的一些其它重要考慮因素包括初始精度和溫度漂移。初始精度以%或mV為單位。許多系統(tǒng)允許校準,因此初始精度不如漂移那么重要,而漂移通常以ppm/°C或µV/°C為單位。大多數(shù)優(yōu)秀的基準電壓源漂移低于10 ppm/°C,而ADR45xx系列更是將漂移驅(qū)動至僅有數(shù)ppm/°C。該漂移必須納入系統(tǒng)誤差預算中。

基準電壓源故障排除

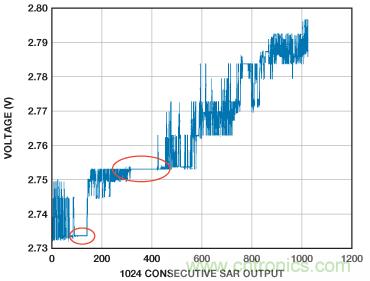

設計不佳的基準電壓源電路可能導致嚴重的轉(zhuǎn)換錯誤。最常見的基準電壓源問題是來自ADC的重復或"粘連"代碼問題。當基準電壓源輸入端噪聲足夠大,便可能造成ADC作出錯誤的位判斷。哪怕輸入有所改變,它也以同樣的代碼重復出現(xiàn)多次,或者在較低的有效位中填充重復的1或0字串,如圖9所示。紅色圓圈區(qū)域中,ADC出現(xiàn)粘連,重復返回相同的代碼。通常滿量程附近的問題更嚴重,因為基準電壓源噪聲對較高有效位的判斷產(chǎn)生的影響更大。一旦作出錯誤的位判斷,其余位便填充1或0。

圖9. ADC傳遞函數(shù)中的"粘連"代碼

導致出現(xiàn)"粘連"位的最常見原因是基準電壓源電容的尺寸與位置、基準電壓源/基準電壓源緩沖器的驅(qū)動能力不足,或是基準電壓源/基準電壓源緩沖器選型不當導致過量噪聲。

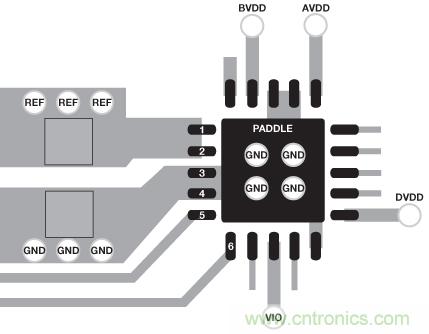

將儲能電容放置在ADC的基準電壓源輸入引腳附近并使用寬走線實現(xiàn)連接很重要,如圖10所示。使用多個過孔將電容連接至接地層,可獲得較低的阻抗路徑。若基準電壓源具有專用地,則電容應當通過寬走線連接至該引腳附近。由于電容用作電荷庫,它必須足夠大,以限制衰減,并且必須具有低ESR特性。具有X5R電介質(zhì)的陶瓷電容是個不錯的選擇。電容典型值為10 µF至47 µF范圍內(nèi),但根據(jù)ADC的電流要求,有時也可使用較小數(shù)值的電容。

圖10. 典型基準電壓源電容布局

驅(qū)動能力不足是另一個問題,特別是使用低功耗基準電壓源或微功耗基準電壓源緩沖器,因為它們通常具有高得多的輸出阻抗,隨頻率而明顯增加。使用吞吐速率較高的ADC時,這個問題尤其明顯,因為吞吐速率較低時,電流要求更高。

來自基準電壓源或基準電壓源緩沖器的過量噪聲與轉(zhuǎn)換器的LSB大小有關(guān),也可能會造成粘連代碼,因此基準電壓源電路的電壓噪聲必須保持為LSB電壓的一小部分。

結(jié)論

本文討論了如何針對精密逐次逼近型ADC設計基準電壓源電路,并強調(diào)了如何判斷某些常見問題。文中的計算公式用于估算基準電壓源電路的驅(qū)動能力和噪聲要求,以便有更高的概率使該電路通過硬件測試。

參考電路

AN-931 Application Note. “Understanding PulSAR ADC Support Circuitry.”

Kester, Walt. Data Conversion Handbook, Chapter 7. “Data Converter Support Circuits.”

Kester, Walt. “Which ADC Architecture Is Right for Your Application?” Analog Dialogue. Volume 39, Number 2, 2005.

Walsh, Alan. “Front-End Amplifier and RC Filter Design for a Precision SAR Analog-to-Digital Converter.” Analog Dialogue. Volume 46, Number 4, 2012.

推薦閱讀: