【導(dǎo)讀】直接數(shù)字頻率合成(DDS)技術(shù)用于產(chǎn)生和調(diào)節(jié)高質(zhì)量波形,廣泛用于醫(yī)學(xué)、工業(yè)、儀器儀表、通信、國(guó)防等眾多領(lǐng)域。本文將簡(jiǎn)要介紹該技術(shù),說(shuō)明其優(yōu)勢(shì)和不足,考察一些應(yīng)用示例,同時(shí)介紹一些有助于該技術(shù)推廣的新產(chǎn)品。

簡(jiǎn)介

許多行業(yè)中一個(gè)關(guān)鍵的需求是精確產(chǎn)生、輕松操作并快速更改不同頻率、不同類(lèi)型的波形。無(wú)論是寬帶收發(fā)器要求具有低相位噪聲和出色的無(wú)雜散動(dòng)態(tài)性能的捷變頻率源,還是工業(yè)測(cè)量和控制系統(tǒng)需要穩(wěn)定的頻率激勵(lì),快速、輕松、經(jīng)濟(jì)地產(chǎn)生可調(diào)波形并同時(shí)維持相位連續(xù)性的能力都是至關(guān)重要的一項(xiàng)設(shè)計(jì)標(biāo)準(zhǔn),而這正是直接數(shù)字頻率合成技術(shù)的優(yōu)勢(shì)所在。

頻率合成的任務(wù)

不斷增多的頻譜擁堵,加上對(duì)功耗更低、質(zhì)量更高的測(cè)量設(shè)備的永無(wú)止境的需求,這些因素都要求使用新的頻率范圍,要求更好地利用現(xiàn)有頻率范圍。結(jié)果,人們尋求對(duì)頻率產(chǎn)生進(jìn)行更好的控制,多數(shù)情況下,均是借助于頻率合成器. 這些器件利用一個(gè)給定頻率, fC,來(lái)產(chǎn)生一個(gè)相關(guān)的目標(biāo)頻率(和相位), fOUT. 其一般關(guān)系可以簡(jiǎn)單地表示為:

fOUT = εx× fC

其中,比例因子εx, 有時(shí)也被稱(chēng)為歸一化頻率.

該等式通常利用實(shí)數(shù)逐步逼近的算法實(shí)現(xiàn)。當(dāng)比例因子為有理數(shù)時(shí),兩個(gè)相對(duì)質(zhì)數(shù)(輸出頻率和基準(zhǔn)頻率)之比將諧波相關(guān)。但在多數(shù)情況下,εx 可能屬于更廣泛的實(shí)數(shù)集,逼近過(guò)程一旦處于可接受的范圍之內(nèi)即會(huì)被截?cái)?/div>

直接數(shù)字頻率合成

頻率合成器的一種實(shí)用型實(shí)現(xiàn)方式是直接數(shù)字頻率合成 (DDFS), 通常簡(jiǎn)稱(chēng)為 直接數(shù)字合成 (DDS). 這種技術(shù)利用數(shù)字?jǐn)?shù)據(jù)處理來(lái)產(chǎn)生一個(gè)頻率和相位可調(diào)的輸出,該輸出與一個(gè)固定的頻率參考或時(shí)鐘源fC.相關(guān)。在DDS架構(gòu)中,參考或系統(tǒng)時(shí)鐘頻率由一個(gè)比例因子分頻來(lái)產(chǎn)生所需頻率,該比例因子由二進(jìn)制調(diào)諧字可編程控制。

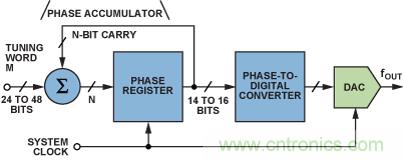

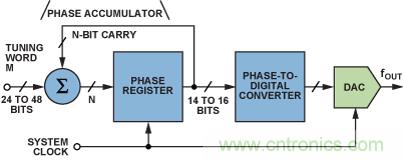

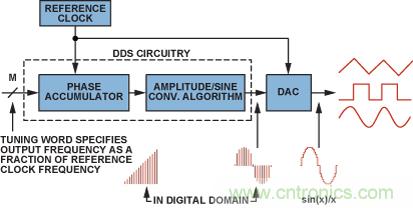

簡(jiǎn)言之,直接數(shù)字頻率合成器將一串時(shí)鐘脈沖轉(zhuǎn)換成一個(gè)模擬波形,通常為一個(gè)正弦波、三角波或方波。如圖1所示,其主要部分為:相位累加器(產(chǎn)生輸出波形相位角度的數(shù)據(jù)), 相數(shù)轉(zhuǎn)換器,(將上述相位數(shù)據(jù)轉(zhuǎn)換為瞬時(shí)輸出幅度數(shù)據(jù)),以及數(shù)模轉(zhuǎn)換器(DAC)(將該幅度數(shù)據(jù)轉(zhuǎn)換成采樣模擬數(shù)據(jù)點(diǎn))

圖1.DDS系統(tǒng)的功能框圖。

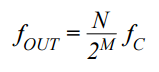

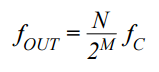

對(duì)于正弦波輸出,相數(shù)轉(zhuǎn)換器通常為一個(gè)正弦查找表(圖2)。相位累加器以N為單位計(jì)數(shù),并根據(jù)以下等式產(chǎn)生一個(gè)相對(duì)于fC的頻率:

其中:

M為調(diào)諧字的分辨率(24至48位)

N為對(duì)應(yīng)于相位累加器輸出字最小增量相位變化的fC的脈沖數(shù).

圖2.典型的DDS架構(gòu)和信號(hào)路徑(帶DAC)。

由于更改N會(huì)立即改變輸出相位和頻率,因此,系統(tǒng)自身具有相位連續(xù),特點(diǎn),這是許多應(yīng)用的關(guān)鍵屬性之一。無(wú)需環(huán)路建立時(shí)間,這與模擬系統(tǒng)不同,如鎖相環(huán) (PLL).

DAC通常為一個(gè)高性能電路,專(zhuān)門(mén)針對(duì)DDS內(nèi)核(相位累加器和相幅轉(zhuǎn)換器)而設(shè)計(jì)。多數(shù)情況下,結(jié)果形成的器件(通常為單芯片)一般稱(chēng)為純DDS或C-DDS。

實(shí)際的DDS器件一般集成多個(gè)寄存器,以實(shí)現(xiàn)不同的頻率和相位調(diào)制方案。如相位寄存器,其存儲(chǔ)的相位內(nèi)容被加在相位累加器的輸出相位上。這樣,可以對(duì)應(yīng)于一個(gè)相位調(diào)諧字延遲輸出正弦波的相位。對(duì)于通信系統(tǒng)相位調(diào)制應(yīng)用,這非常有用。加法器電路的分辨率決定著相位調(diào)諧字的位數(shù),因此,也決定著延遲的分辨率。

在單個(gè)器件上集成一個(gè)DDS引擎和一個(gè)DAC既有優(yōu)點(diǎn)也有缺點(diǎn),但是,無(wú)論集成與否,都需要一個(gè)DAC來(lái)產(chǎn)生純度超高的高品質(zhì)模擬信號(hào)。DAC將數(shù)字正弦輸出轉(zhuǎn)換為一個(gè)模擬正弦波,可能是單端,也可能是差分。一些關(guān)鍵要求是低相位噪聲、優(yōu)秀的寬帶(WB)和窄帶(NB)無(wú)雜散動(dòng)態(tài)范圍 (SFDR)以及低功耗。如果是外部器件,則DAC必須足夠快以處理信號(hào),因此,內(nèi)置并行端口的器件非常常見(jiàn)。

DDS與其他解決方案

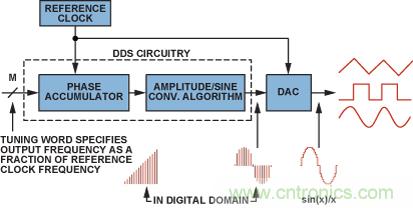

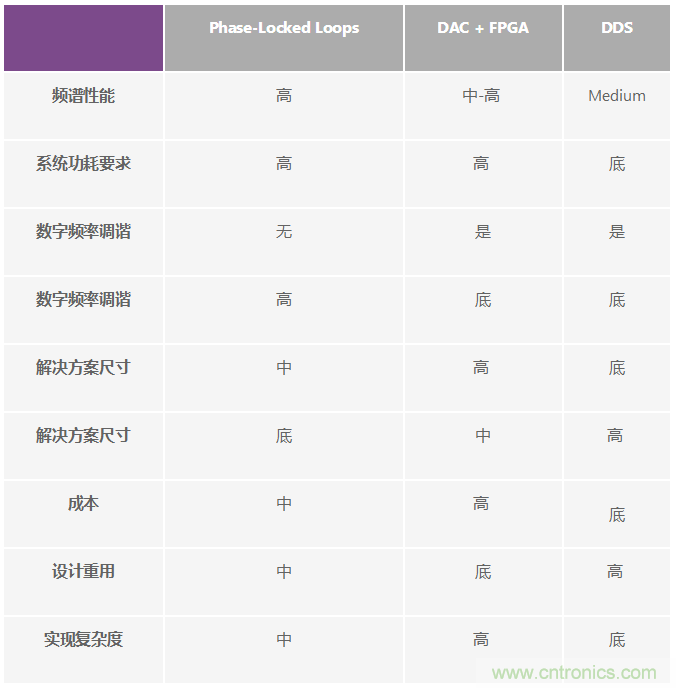

其他產(chǎn)生頻率的方法包括模擬鎖相環(huán)(PLL),時(shí)鐘發(fā)生器和利用FPGA對(duì)DAC的輸出進(jìn)行動(dòng)態(tài)編程。通過(guò)考察頻譜性能和功耗,可以對(duì)這些技術(shù)進(jìn)行簡(jiǎn)單的比較,表1以定性方式展示了比較結(jié)果

表1.DDS與競(jìng)爭(zhēng)技術(shù)——高級(jí)比較

鎖相環(huán)是一種反饋環(huán)路,其組成部分為:一個(gè)相位比較器, 一個(gè)除法器和一個(gè)壓控制振蕩器 (VCO). 相位比較器將基準(zhǔn)頻率與輸出頻率(通常是輸出頻率的N)分頻)進(jìn)行比較。相位比較器產(chǎn)生的誤差電壓用于調(diào)節(jié)VCO,從而輸出頻率。當(dāng)環(huán)路建立后,輸出將在頻率和/或相位上與參考頻率保持一種精確的關(guān)系。PLL長(zhǎng)期以來(lái)一直被認(rèn)為是在特定頻帶范圍內(nèi)要求高保真度和穩(wěn)定信號(hào)的低相位噪聲和高無(wú)雜散動(dòng)態(tài)范圍 (SFDR) 應(yīng)用的理想選擇.

由于PLL無(wú)法精確、快速地調(diào)諧頻率輸出和波形,而且響應(yīng)較慢,這限制了它們對(duì)于快速跳頻和部分頻移鍵控和相移鍵控應(yīng)用的適用性.

其他方案,包括集成DDS引擎的現(xiàn)場(chǎng)可編程門(mén)陣列 (FPGAs) ——配合現(xiàn)成DAC以合成輸出正弦波——雖然可以解決PLL的跳頻問(wèn)題,但也存在自身的缺陷。主要系統(tǒng)缺陷包括較高的工作和接口功耗要求、成本較高、尺寸較大,而且系統(tǒng)開(kāi)發(fā)人員還須考慮額外的軟件、硬件和存儲(chǔ)器問(wèn)題。例如,利用現(xiàn)代FPGA中的DDS引擎選項(xiàng),要產(chǎn)生動(dòng)態(tài)范圍為60 dB的10 MHz輸出信號(hào),需要多達(dá)72 kB的存儲(chǔ)器空間。另外,設(shè)計(jì)師需要接受并熟悉細(xì)微權(quán)衡和DDS內(nèi)核的架構(gòu)。

從實(shí)用角度來(lái)看(見(jiàn)表2),得益于CMOS工藝和現(xiàn)代數(shù)字設(shè)計(jì)技術(shù)的快速發(fā)展以及DAC拓?fù)浣Y(jié)構(gòu)的改進(jìn),DDS技術(shù)已經(jīng)能在廣泛的應(yīng)用中實(shí)現(xiàn)前所未有的低功耗、頻譜性能和成本水平。雖然純DDS產(chǎn)品不可能在性能和設(shè)計(jì)靈活性上達(dá)到高端DAC技術(shù)與FPGA相結(jié)合的水平,但DDS在尺寸、功耗、成本和簡(jiǎn)單性方面的優(yōu)勢(shì)使其成為許多應(yīng)用的首要選擇。

表2.基準(zhǔn)分析小結(jié)——頻率產(chǎn)生技術(shù)(<50 MHz)

同時(shí)需要指出,由于DDS器件從根本上來(lái)說(shuō)是用數(shù)字方法產(chǎn)生輸出波形,因此它可以簡(jiǎn)化一些解決方案的架構(gòu),或者為對(duì)波形進(jìn)行數(shù)字化編程創(chuàng)造條件。盡管通常利用正弦波來(lái)解釋DDS的功能和工作原理,但利用現(xiàn)代DDS IC也可以輕松產(chǎn)生三角波或方波(時(shí)鐘)輸出,由此消除了前一種情況的查找表以及后一種情況的DAC的必要性,因?yàn)榧梢粋€(gè)簡(jiǎn)單而精確的比較器就夠了.

DDS的性能與限制

Images and Envelopes: Sin(x)/x Roll-Off

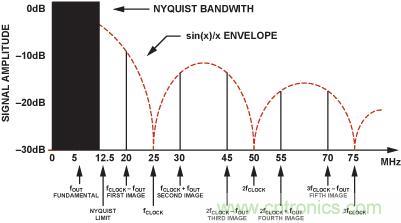

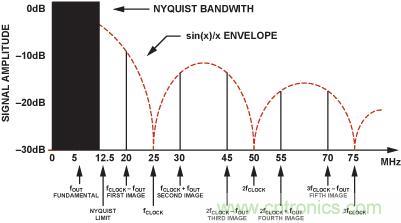

DAC的實(shí)際輸出不是連續(xù)的正弦波,而是帶有正弦時(shí)間包絡(luò)的一系列脈沖。對(duì)應(yīng)的頻譜是一系列圖像和混疊信號(hào)。圖像沿sin(x)/x 包絡(luò)分布(見(jiàn)圖3中的|幅度|曲線(xiàn)圖)。有必要進(jìn)行濾波,以抑制目標(biāo)頻帶之外的頻率,但是不能抑制通帶中出現(xiàn)的高階混疊(例如,因DAC非線(xiàn)性所致)

奈奎斯特準(zhǔn)則 要求,每個(gè)周期至少需要兩個(gè)采樣點(diǎn)才能重建所需輸出波形。鏡像響應(yīng)產(chǎn)生于采樣輸出頻率中 K fCLOCK × fOUT. 在本例中,其中 fCLOCK = 25 25 MHz且 fOUT = 5 MHz,第一和第二鏡頻出現(xiàn)在(見(jiàn)圖3)fCLOCK × fOUT, o即20 MHz和30 MHz。第三和第四鏡頻出現(xiàn)在45 MHz和55 MHz。注意,sin(x)/x零值出現(xiàn)在采樣頻率的倍數(shù)處。當(dāng)fOUT 大于奈奎斯特帶寬 (1/2 fCLOCK), 時(shí),第一鏡頻將出現(xiàn)于奈奎斯特帶寬之內(nèi),發(fā)生混疊(例如,15 MHz的信號(hào)將向下混疊至10 MHz)。無(wú)法用傳統(tǒng)的奈奎斯特抗混疊濾波器從輸出中濾掉混疊鏡頻

圖3.DDS中的Sin(x)/x滾降。

在典型的DDS應(yīng)用中,利用一個(gè)低通濾波器來(lái)抑制輸出頻譜中鏡頻響應(yīng)的影響。為了使低通濾波器的截止頻率要求保持于合理水平,并使濾波器設(shè)計(jì)保持簡(jiǎn)單,一種可行的做法是利用一個(gè)經(jīng)濟(jì)的低通輸出濾波器將fOUT 帶寬限制在fCLOCK頻率的40%左右.

任何給定鏡頻相對(duì)于基波的幅度可用sin(x)/x公式來(lái)計(jì)算。由于該函數(shù)隨頻率滾降,因此基本輸出的幅度將與輸出頻率成反比而降低;在DDS系統(tǒng)中,降低量為DC-奈奎斯特帶寬范圍的–3.92 dB。

第一鏡頻的幅度較大——基波的3 dB范圍內(nèi)。為了簡(jiǎn)化DDS應(yīng)用的濾波要求,必須制定頻率計(jì)劃,并分析鏡頻和sin(x)/x幅度響應(yīng)在fOUT和fCLOCK目標(biāo)頻率下的頻譜要求。在線(xiàn)互動(dòng)設(shè)計(jì)工具 支持ADI DDS產(chǎn)品系列,可以快速、輕松地仿真鏡像頻率大小,并允許用戶(hù)選擇鏡像位于目標(biāo)頻帶之外的頻率。更多有用信息,請(qǐng)參閱更多信息和有用的鏈接部分.

輸出頻譜中的其他不需要的頻率(如DAC的積分和微分線(xiàn)性誤差、與DAC相關(guān)的突波能量和時(shí)鐘饋通噪聲)不會(huì)遵循sin(x)/x滾降響應(yīng)。這些不需要的頻率將以諧波和雜散能量出現(xiàn)在輸出頻譜中的許多地方——但其幅度一般會(huì)遠(yuǎn)遠(yuǎn)低于鏡頻響應(yīng)。DDS器件的一般本底噪聲由基板噪聲、熱噪聲效應(yīng)、接地耦合和其他信號(hào)源耦合等因素累積組合決定。DDS器件的本底噪聲、性能雜散和抖動(dòng)受到電路板布局、電源質(zhì)量以及——最重要的是——輸入?yún)⒖紩r(shí)鐘質(zhì)量的深刻影響。

抖動(dòng)

完美時(shí)鐘源的邊沿將以精確的時(shí)間間隔發(fā)生,而該間隔永遠(yuǎn)都不會(huì)變化。當(dāng)然,這是不可能的;即使最好的振蕩器也是由不理想的元件構(gòu)成,具有噪聲等缺陷。優(yōu)質(zhì)的低相位噪聲晶體振蕩器的抖動(dòng)為皮秒級(jí),而且是從數(shù)百萬(wàn)個(gè)時(shí)鐘邊沿累積起來(lái)的。導(dǎo)致抖動(dòng)的因素有熱噪聲、振蕩器電路不穩(wěn)定以及電源、接地和輸出連接等帶來(lái)的外部干擾等,所有這些因素都會(huì)干擾振蕩器的時(shí)序特性。另外,振蕩器受外部磁場(chǎng)或電場(chǎng)以及附近發(fā)射器的射頻干擾的影響。振蕩器電路中,一個(gè)簡(jiǎn)單的放大器、反相器或緩沖器也都會(huì)給信號(hào)帶來(lái)額外的抖動(dòng)。

因此,選擇一個(gè)抖動(dòng)低、邊沿陡的穩(wěn)定的參考時(shí)鐘振蕩器是至關(guān)重要的。較高頻率的基準(zhǔn)時(shí)鐘允許較大的過(guò)采樣,而且,通過(guò)分頻可以在一定程度上減輕抖動(dòng),因?yàn)閷?duì)信號(hào)進(jìn)行分頻將在更長(zhǎng)時(shí)期產(chǎn)生相同量的抖動(dòng),因而可以降低信號(hào)上的抖動(dòng)的百分比。

噪聲——包括相位噪聲

采樣系統(tǒng)的噪聲取決于諸多因素,首要因素是參考時(shí)鐘抖動(dòng),這種抖動(dòng)表現(xiàn)為基波信號(hào)上的相位噪聲。在DDS系統(tǒng)中,截?cái)嘞辔患拇嫫鬏敵隹赡軒?lái)因代碼而異的系統(tǒng)誤差。二進(jìn)制字不會(huì)導(dǎo)致截?cái)嗾`差。但對(duì)于非二進(jìn)制字,相位噪聲截?cái)嗾`差會(huì)在頻譜中產(chǎn)生雜散。雜散的頻率/幅度取決于代碼字。DAC的量化和線(xiàn)性誤差也會(huì)給系統(tǒng)帶來(lái)諧波噪聲。時(shí)域誤差(如欠沖/過(guò)沖和代碼錯(cuò)誤)都會(huì)加重輸出信號(hào)的失真.

應(yīng)用

DDS應(yīng)用可以分為兩大類(lèi):

● 要求捷變頻率源以進(jìn)行數(shù)據(jù)編碼和調(diào)制應(yīng)用的通信和雷達(dá)系統(tǒng)

● 要求通用頻率合成功能以及可編程調(diào)諧、掃描和激勵(lì)能力的測(cè)量、工業(yè)和光學(xué)應(yīng)用

兩種情況下,都出現(xiàn)了一種走向更高頻譜純度(更低的相位噪聲和更高的無(wú)雜散動(dòng)態(tài)范圍)的趨勢(shì),同時(shí)還存在低功耗和小尺寸的要求,以適應(yīng)遠(yuǎn)程或電池供電設(shè)備的需求。

調(diào)制/數(shù)據(jù)編碼和同步中的DDS

DDS產(chǎn)品首先出現(xiàn)于雷達(dá)和軍事應(yīng)用之中,其部分特性的發(fā)展(性能的提升、成本和尺寸等)已使DDS技術(shù)在調(diào)制和數(shù)據(jù)編碼應(yīng)用中日漸盛行。本節(jié)將討論兩種數(shù)據(jù)編碼方案及其在DDS系統(tǒng)中的實(shí)現(xiàn)方式

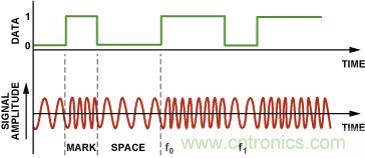

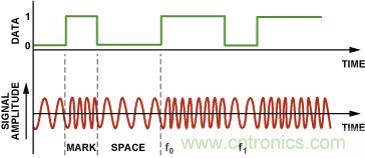

圖4.二進(jìn)制FSK調(diào)制。

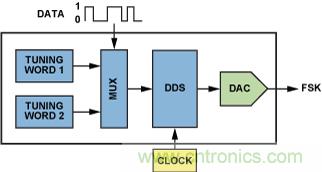

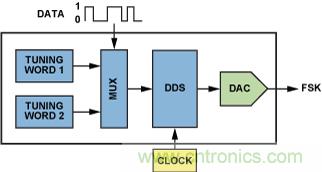

二進(jìn)制1和0表示為兩個(gè)不同的頻率,分別為f0和f1。這種編碼方案可以輕松在DDS器件中實(shí)現(xiàn)。代表輸出頻率的DDS頻率調(diào)諧字被改變,以從將發(fā)射的1和0產(chǎn)生f0和f1。在ADI純DDS產(chǎn)品系列中,至少有兩款器件AD9834和AD9838—另見(jiàn)附錄),用戶(hù)可以簡(jiǎn)單地將兩個(gè)當(dāng)前FSK頻率調(diào)諧字編程進(jìn)IC的嵌入式頻率寄存器之中。要變換輸出頻率,則須用專(zhuān)用的引腳FSELECT選擇含有相應(yīng)調(diào)諧字的寄存器(見(jiàn)圖5)

圖5.利用AD9834或AD9838 DDS的調(diào)諧字選擇器實(shí)現(xiàn)FSK編碼。

相移鍵控(PSK)是另一種簡(jiǎn)單的數(shù)據(jù)編碼形式。在PSK中,載波的頻率保持不變,通過(guò)改變發(fā)射信號(hào)的相位來(lái)傳遞信息。可以利用多種方案來(lái)實(shí)現(xiàn)PSK。最簡(jiǎn)單的方法通常稱(chēng)為二進(jìn)制PSK(即BPSK),只采用兩個(gè)信號(hào)相位:0°(邏輯1)和180°(邏輯0)。各位的狀態(tài)取決于前一位的狀態(tài)。如果波的相位不變,則信號(hào)狀態(tài)將保持不變(低或高)。如果波的相位改變180°,即相位反轉(zhuǎn),則信號(hào)狀態(tài)將改變(低變?yōu)楦?,或高變?yōu)榈停SK編碼可以輕松在DDS產(chǎn)品中實(shí)現(xiàn),因?yàn)槎鄶?shù)器件都有一個(gè)獨(dú)立的輸入寄存器(相位寄存器),可以加載相位值。該值被直接添加到載波的相位,而不改變其頻率。更改該寄存器的內(nèi)容將調(diào)制載波的相位,結(jié)果產(chǎn)生一個(gè)PSK輸出。對(duì)于要求高速調(diào)制的應(yīng)用,內(nèi)置相位寄存器對(duì)的AD9834和AD9838允許其PSELECT引腳上的信號(hào)在預(yù)加載的相位寄存器之間變換,以根據(jù)需要調(diào)制載波。

更復(fù)雜的PSK采用四個(gè)或八個(gè)波相位。這樣,每當(dāng)相位發(fā)生變化時(shí),二進(jìn)制數(shù)據(jù)的傳輸速率將高于BPSK調(diào)制。在四相位調(diào)制 (正交 PSK),中,可能的相位角度為0°, +90°, −90°, 和 +180°;每次相位變換可能代表兩個(gè)信號(hào)因子AD9830, AD9831, AD9832, 和 AD9835 提供四個(gè)相位寄存器,通過(guò)連續(xù)更新寄存器的不同相位偏移,可以實(shí)現(xiàn)復(fù)雜的相位調(diào)制方案.

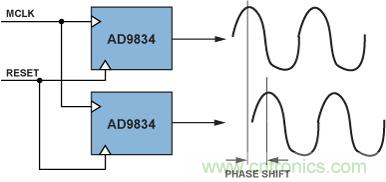

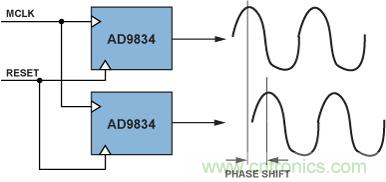

以同步模式利用多個(gè)DDS元件實(shí)現(xiàn)I/Q功能

許多應(yīng)用要求產(chǎn)生兩個(gè)或兩個(gè)以上具有已知相位關(guān)系的正弦波或方波信號(hào)。一個(gè)常見(jiàn)的例子是同相和正交調(diào)制(I/Q),在這種技術(shù)中,在0°和90°相位角度從載波頻率獲得信號(hào)信息??梢杂孟嗤脑磿r(shí)鐘來(lái)運(yùn)行兩個(gè)單獨(dú)的DDS元件,以輸出可以直接控制和操作其相位關(guān)系的信號(hào)。在圖6中,用一個(gè)基準(zhǔn)時(shí)鐘對(duì)AD9838器件編程;相同的RESET引腳用于更新兩個(gè)器件。這樣,可以實(shí)現(xiàn)簡(jiǎn)單的I/Q調(diào)制

RESET必須在上電后以及向DDS傳輸任何數(shù)據(jù)之前初始化。結(jié)果可將DDS輸出置于已知相位,使其成為共同的參考角度,以便同步多個(gè)DDS器件。當(dāng)新數(shù)據(jù)被同時(shí)送至多個(gè)DDS器件時(shí),DDS之間可以保持相關(guān)相位關(guān)系,或者通過(guò)相位偏移寄存器可以預(yù)測(cè)性調(diào)整多個(gè)DDS之間的相對(duì)相位偏移。AD983x系列DDS產(chǎn)品擁有12位相位分辨率,有效分辨率為0.1°。

圖6.同步兩個(gè)DDS元件。

有關(guān)同步多個(gè)DDS器件的更多信息,請(qǐng)參閱應(yīng)用筆記 AN-605同步多個(gè)基于DDS的頻率合成器AD9852..

網(wǎng)絡(luò)分析

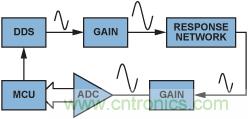

電子世界中的諸多應(yīng)用都需要收集和解碼來(lái)自網(wǎng)絡(luò)的數(shù)據(jù),例如模擬測(cè)量和光學(xué)通信系統(tǒng)。正常情況下,系統(tǒng)分析要求是為了以幅度和相位已知的頻率模擬電路或系統(tǒng),并分析通過(guò)系統(tǒng)的響應(yīng)信號(hào)的特性.

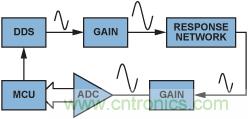

對(duì)響應(yīng)信號(hào)收集的信息用于確定關(guān)鍵系統(tǒng)信息。測(cè)試網(wǎng)絡(luò)的范圍(見(jiàn)圖7)可能非常寬泛,包括電纜完整性測(cè)試、生物醫(yī)學(xué)傳感和流速測(cè)量系統(tǒng)。無(wú)論何時(shí),只要基本要求是產(chǎn)生基于頻率的信號(hào)并將響應(yīng)信號(hào)的相位和幅度與原始信號(hào)進(jìn)行比較,或者是要通過(guò)系統(tǒng)激勵(lì)一系列頻率,或者要求具有不同相位關(guān)系(如具有I/Q功能的系統(tǒng)中)的測(cè)試信號(hào),則可利用直接數(shù)字頻率合成IC,方便、優(yōu)雅地通過(guò)軟件以數(shù)字方式控制激勵(lì)頻率和相位。

圖7.利用頻率激勵(lì)的典型網(wǎng)絡(luò)分析架構(gòu)。

電纜完整性/損耗測(cè)量

纜完整性測(cè)量是一種非介入式電纜分析方法,廣泛用于飛機(jī)布線(xiàn)、局域網(wǎng)(LAN)和電話(huà)線(xiàn)路等應(yīng)用之中。確定性能的一種方式是看通過(guò)電纜時(shí)損耗了多少信號(hào)。通過(guò)注入頻率和幅度已知的信號(hào),用戶(hù)可以在電纜遠(yuǎn)端測(cè)量幅度和相位,由此算出電纜衰減。直流電阻和特性阻抗等參數(shù)將影響具體電纜的衰減。其結(jié)果通常表示為在整個(gè)測(cè)試頻率范圍內(nèi)低于信號(hào)源的(0 dB)分貝數(shù)。目標(biāo)頻率取決于電纜類(lèi)型。DDS器件因具有產(chǎn)生寬范圍頻率的能力,所以可以用作具有必要頻率分辨率的激勵(lì)。

流量計(jì)

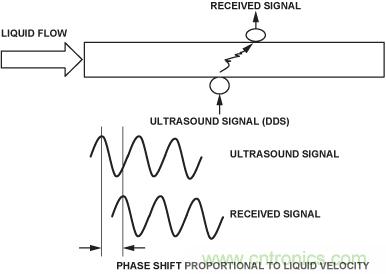

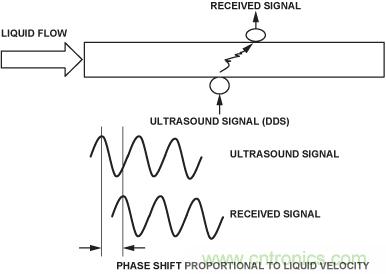

一種相關(guān)應(yīng)用是對(duì)管道中的水、其他液體和氣體進(jìn)行流量分析。一個(gè)例子是超聲流量測(cè)量,其工作原理是相移原則,如圖8所示。基本而言,從有液體流動(dòng)的通道的一端發(fā)射信號(hào),同時(shí)在另一端放置一個(gè)傳感器以測(cè)量相位響應(yīng)(取決于流速)。這種技術(shù)存在多種變化。測(cè)試頻率取決于測(cè)量的物質(zhì);一般而言,往往在一系列頻率范圍內(nèi)發(fā)射輸出信號(hào)。DDS具有無(wú)縫設(shè)置和更改頻率的靈活性

圖8.超聲流量計(jì)。

更多信息和有用的鏈接

互動(dòng)式設(shè)計(jì)工具

它是什么?它是DDS的在線(xiàn)互動(dòng)式設(shè)計(jì)工具,是在給定參考時(shí)鐘和目標(biāo)輸出頻率和/或相位時(shí)用于選擇調(diào)諧字的輔助工具。該工具的編程計(jì)算結(jié)果給出了調(diào)諧字和其他配置位,供對(duì)器件串行接口編程時(shí)使用。在應(yīng)用外部重構(gòu)濾波器之后,可以顯示選定參考時(shí)鐘和輸出頻率的理想輸出諧波。ADI設(shè)計(jì)工具的鏈接可以在互動(dòng)式設(shè)計(jì)工具主頁(yè)上找到AD9834設(shè)計(jì)工具即是例子之一.

評(píng)估套件

AD983x系列產(chǎn)品配備功能完善的評(píng)估套件,并配有原理圖和布局指南。借助評(píng)估套件中提供的軟件,用戶(hù)可以輕松對(duì)器件進(jìn)行編程、配置和測(cè)試(見(jiàn)圖9)

圖9.AD9838評(píng)估軟件接口。

其他有用的DDS信號(hào)可以在DDS網(wǎng)站上找到.

另請(qǐng)參閱:

Murphy, Eva and Colm Slattery. "直接數(shù)字頻率合成全攻略." 應(yīng)用工程師問(wèn)答—33。模擬對(duì)話(huà)。2004年第38卷第3期: 8–12.

數(shù)字信號(hào)合成技術(shù)教程.. 1999. Analog Devices, Inc.

附錄

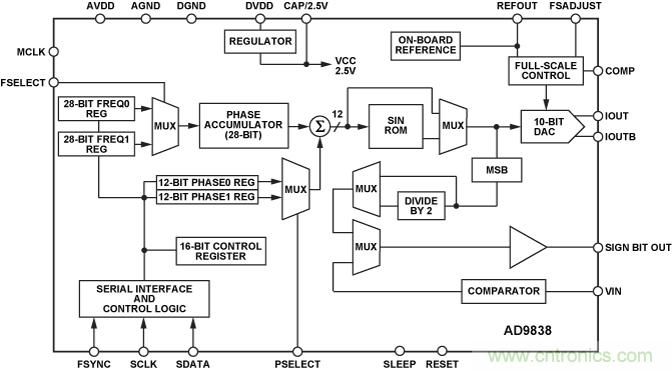

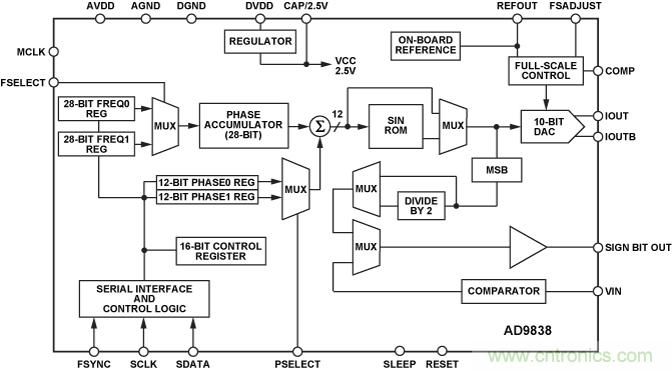

AD9838簡(jiǎn)介:AD9838 DDS的功能框圖如圖10所示。該器件采用細(xì)線(xiàn)CMOS工藝制成,是一款超低功耗(11 mW)的純DDS。28位的頻率寄存器支持0.06 Hz頻率分辨率和16 MHz時(shí)鐘,以及0.02 Hz頻率分辨率和5 MHz時(shí)鐘。相位和頻率調(diào)制通過(guò)片內(nèi)寄存器利用軟件或引腳選擇來(lái)配置。該器件具有−68 dBc寬帶和−97 dBc窄帶SFDR,工作溫度范圍為–40°C至+125°C擴(kuò)展溫度范圍。器件采用小型4 mm × 4 mm、20引腳LFCSP(引腳架構(gòu)芯片級(jí))封裝.

圖10.AD9838 DDS的功能框圖。

推薦閱讀: