【導讀】所有數(shù)模轉換器(DAC)都提供與數(shù)字設置增益和所施加基準 電壓之積成比例的輸出。乘法DAC與固定基準電壓DAC不 同,因為它可以將高分辨率數(shù)字設置增益應用施加到可變帶寬 模擬信號上。本文將討論電阻梯乘法DAC及其對交流信號處 理應用的適用性。

基本原理

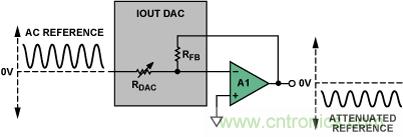

從1974, 年ADI公司推出世界首款(10 位)CMOS IC乘法DAC 以來,ADI公司就一直是乘法DAC設計與生產(chǎn)的領先者。它們 采用一個具有適當帶寬的放大器,利用一個切換式R-2R梯和 一個片內反饋電阻實現(xiàn)了調整交流增益或可變直流基準電壓 輸入信號增益的簡單方法,從而用DAC取代了典型反相運算 放大器級的輸入和反饋電阻(圖 1)。數(shù)字調整電阻梯和片內 反饋電阻一起,提供與數(shù)字輸入成比例的增益(D/2n)使RDAC 起 到了可變輸入電阻的作用。

圖 1. 反相增益配置

乘法DAC的市場發(fā)展迅速,歷經(jīng)數(shù)代更新,產(chǎn)品的分辨率、 精度和速度有了大幅提升,增加了各種數(shù)字存儲功能、串行通 信選項,尺寸和成本大大降低并且每個芯片上還可以配置額外的DAC。最新一代的乘法DAC提供理想的構建模塊,用于控 制可變直流或快速交流電壓信號的增益。

電阻(R-2R)梯用于運算放大器反饋電路,提供數(shù)字控制電流, 電流經(jīng) RFB轉換成輸出電壓。放大器以低阻抗提供此輸出?;?準電壓輸入具有恒定的對地電阻R。圖 2 顯示了該工作原理。 圖 2a中,源電流VREF/R, 轉換成輸出電壓。放大器以低阻抗提供此輸出?;?準電壓輸入具有恒定的對地電阻R。圖 2 顯示了該工作原理。 圖 2a中,源電流 IOUT1, 或導引至地(一般稱 IOUT2).同理,剩余電流的一半由開關S2 導引……如此類推。如果開關由一個 數(shù)字字D(S1 是MSB)激活,則流經(jīng)RFB (=R)的IOUT1端電流之 和為 D × 2–n × VREF/R. 此配置的重要優(yōu)勢包括:可最大程度地 降低瞬態(tài),因為開關在地和虛地之間切換;RFB 與梯形電阻片內匹配,具備出色的溫度跟蹤性能。

圖 2. a) R-2R梯原理;b) 乘法DAC, VOUT = 0 to −VREF.

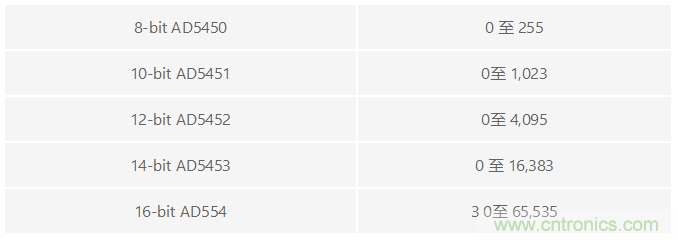

數(shù)字字D給出的數(shù)值范圍取決于所用的器件。ADI公司的部 分AD545x/AD554x系列乘法DAC的D值范圍(第一象限)如下:

提高增益

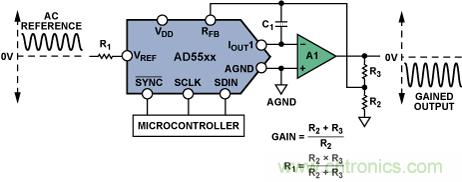

對于輸出電壓必須大于VIN的應用,可通過在DAC級后面增加外部放大器來提高增益;或者只需通過衰減反饋電壓在單級中實現(xiàn),如圖 3 所示。所示近似值對R2||R3<<RFB. R2 和R3應具有相似的溫度系數(shù),但如果R2||R3 與RFB相比較小,則其無需與DAC的溫度系數(shù)相匹配。

圖 3. 提高乘法 DAC 的增益

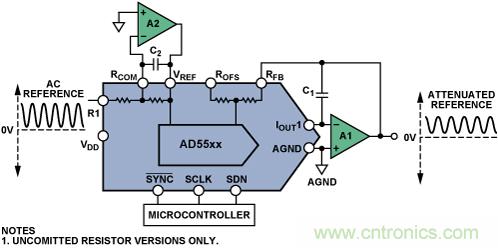

正輸出

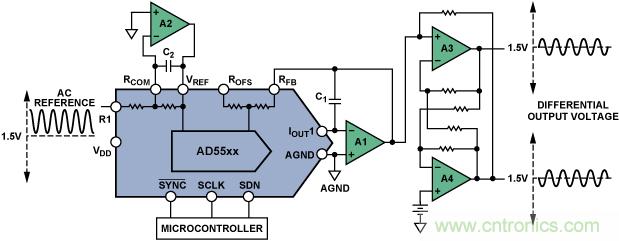

要產(chǎn)生正電壓輸出,可以使用一個外部反相運算放大器電路來 另外反轉輸入或輸出。 一些乘法DAC內置非專用匹配電阻(具 有跟蹤溫度系數(shù)),因此只需額外連接一個運算放大器(圖 4 中的 A2)即可獲得正輸出,這個額外的運算放大器可以是一 個雙通道器件內的配套運算放大器。

如果要求差分輸出,則需要兩個額外的運算放大器。請訪問 www.analog.com/CN-0143Circuits from the Lab® CN-0143查看完整的詳細信息。

圖 4. 乘法DAC, VOUT = 0 to VREF. AD5415、AD5405、AD5546/AD5556、AD5547/AD5557 內置此處所示的非專用電阻

圖 5. 單端-差分

穩(wěn)定性問題

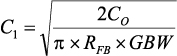

圖 2 和圖 3 中顯示的一個重要元件是補償電容 (C1). 電阻梯的輸出電容加上放大器的輸入電容及任何雜散電容,會在開環(huán)響應中產(chǎn)生極點——這會在環(huán)路閉合時引起振鈴或不穩(wěn)定。為了補償這一點,通常與DAC的內部RFB并聯(lián)連接一個外部反饋電容 C1。如果C1值過小, 會在輸出端產(chǎn)生過沖或振鈴,而值過大 則會過分降低系統(tǒng)帶寬。DAC的內部輸出電容隨碼而變化,因此C1很難確定精確值。根據(jù)以下等式可計算出其最佳近似 值:

其中GBW是運算放大器的最小信號單位增益帶寬乘積,CO 是 DAC的輸出電容。

信號調理的關鍵 M-DAC規(guī)格

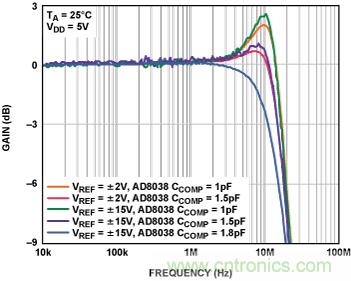

乘法帶寬:增益為–3 dB時的基準電壓輸入頻率。對于給定器件,它與幅度和選擇的補償電容呈函數(shù)關系。圖 6 所示為可以使最高12 MHz的信號相乘的電流輸出DAC AD5544、AD5554或AD545x的乘法帶寬坐標圖。配套的低功耗運算放大器 AD8038具備350 MHz帶寬, 可確保該運算放大器在此范圍內不會引起明顯的動態(tài)誤差。

圖 6. 乘法帶寬

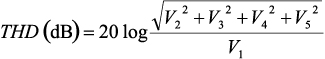

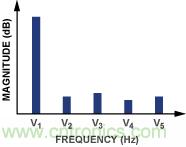

模擬總諧波失真(THD):乘法波形信號中諧波成分的數(shù)學表達。 它近似等于DAC輸出的前四個諧波 (V2, V3, V4, 和 V5)之均方根 和與基波值V1(如圖7所示)的對數(shù)比,計算公式如下:

圖 7. 諧波失真分量

乘法饋通誤差:DAC的數(shù)字輸入全部為0時,由基準電壓輸入至DAC輸出的容性饋通所致的誤差。理想情況下,一直到最低有效位DB0,每下降一位,增益便降低6 dB(圖 8)。 不過,對于較低的位,容性饋通影響增益的頻率更高。這一點 從較低位尾部上翹的平坦曲線可以看出。例如,14位DAC的DB2處,所有頻率的理想增益應為–72 dB,但由于饋通效應,1MHz時的實際增益為–66 dB。

圖 8. 乘法饋通誤差

選擇正確的運算放大器

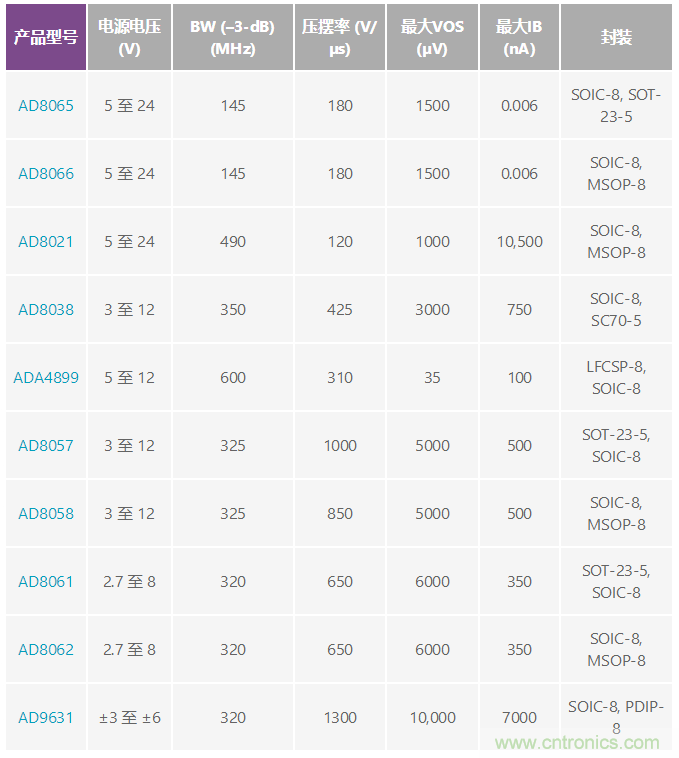

乘法DAC電路性能非常依賴于所選運算放大器的能力,從而 在電阻梯輸出端保持零電壓,并實現(xiàn)電流電壓轉換。要實現(xiàn)最 佳的直流精度,重要的是要選擇具有低失調電壓和偏置電流的運算放大器,以保持誤差與DAC的分辨率相當。詳細的運算 放大器技術規(guī)格參見器件數(shù)據(jù)手冊。

對于基準電壓輸入為較高速信號的應用,需要一個帶寬較寬、 壓擺率較高的運算放大器,以免削弱信號。一個運算放大器電路的增益-帶寬受反饋網(wǎng)絡的阻抗水平和增益配置限制。要確定所需的GBW,一種可行的方式是選擇–3 dB帶寬(10 倍于基準信號頻率)的運算放大器。

必須考慮運算放大器的壓擺率規(guī)格,以限制高頻大信號的失真。對于AD54xx和AD55xx系列,壓擺率為100 V/µs的運算放大器一般就夠了。

表 1 列出了可供乘法應用選擇的運算放大器。

查找適合的 DAC

欲了解可以查看M-DAC的數(shù)模轉換器產(chǎn)品選型表,請訪問 www.analog.com/en/digital-to-analog-converters/da-converters/products/index.html.

結論

自首款CMOS M-DAC問世以來的近40年間,相關器件不斷更新?lián)Q代,許多新的功能特性層出不窮,性能持續(xù)提升,成本和尺寸則大幅縮減。我們的高分辨率、14位/16位電流輸出DAC產(chǎn)品系列AD55xx的最新性能改進包括:

● 積分非線性(INL)性能提高,±1 LSB

● 模擬THD和乘法饋通降低——乘法帶寬增加

● 數(shù)字信號THD降低;可變基準電壓(直流)應用的中間電平突波和數(shù)字饋通降低。

進一步閱讀

1. Kester, Walt, The Data Conversion Handbook (2005) Newnes (Elsevier).

推薦閱讀: