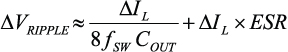

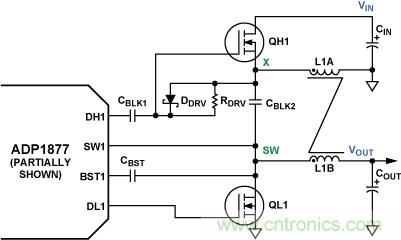

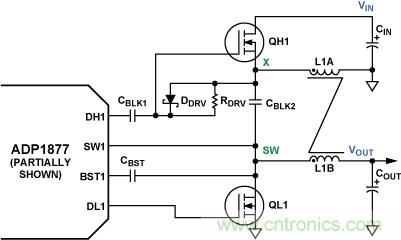

【導(dǎo)讀】許多市場對(duì)高效率同相 DC-DC 轉(zhuǎn)換器的需求都在不斷增長,這些轉(zhuǎn)換器能以降壓或升壓模式工作,即可以將輸入電壓降低或提高至所需的穩(wěn)定電壓��,并且具有最低的成本和最少的元件數(shù)量。反相 SEPIC(單端初級(jí)電感轉(zhuǎn)換器)也稱為 Zeta 轉(zhuǎn)換器,具有許多支持此功能的特性(圖 1)。對(duì)其工作原理及利用雙通道同步開關(guān)控制器ADP1877的實(shí)施方案進(jìn)行分析����,可以了解其在本 應(yīng)用中的有用特性�。

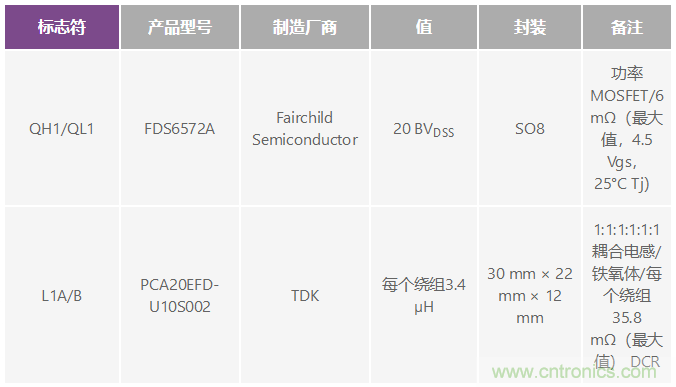

圖1. 反相 SEPIC 拓?fù)浣Y(jié)構(gòu)

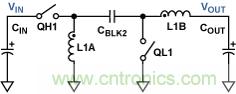

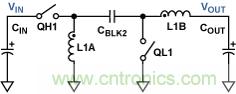

初級(jí)開關(guān)QH1 和次級(jí)開關(guān)QL1 反相工作。在導(dǎo)通時(shí)間內(nèi)��,QH1接通��,QL1 斷開���。電流沿兩條路徑流動(dòng),如圖 2 所示����。第一條路徑是從輸入端經(jīng)過初級(jí)開關(guān)、能量傳輸電容(CBLK2)�����、輸出電感(L1B)和負(fù)載,最終通過地流回輸入端�����。第二條路徑是從輸入端經(jīng)過初級(jí)開關(guān)�����、地基準(zhǔn)電感(L1A)和地流回輸入端��。

圖 2. 電流流向圖����;QH1 閉合,QL1 斷開�����。

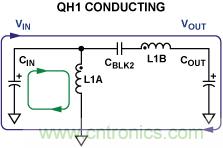

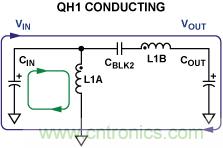

在關(guān)斷期間���,開關(guān)位置剛好相反����。QL1 接通,QH1 斷開����。輸入電容(CIN)斷開,但電流繼續(xù)經(jīng)過電感沿兩條路徑流動(dòng)���,如圖 3所示��。第一條路徑是從輸出電感經(jīng)過負(fù)載��、地和次級(jí)開關(guān)流回輸出電感�����。第二條路徑是從地基準(zhǔn)電感經(jīng)過能量傳輸電容���、次級(jí)開關(guān)流回地基準(zhǔn)電感。

圖 3. 能量傳輸圖�;QL1 閉合,QH1 斷開����。

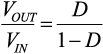

應(yīng)用電感伏秒平衡原理和電容電荷平衡原理����,可以求得方程式 1所規(guī)定的均衡直流轉(zhuǎn)換比���,其中 D 為轉(zhuǎn)換器的占空比(一個(gè)周期的導(dǎo)通時(shí)間部分)。

(1)

上式表明:如果占空比大于 0.5�,輸出端將獲得較高的調(diào)節(jié)電壓(升壓);如果占空比小于 0.5�����,調(diào)節(jié)電壓會(huì)較低(降壓)���。此外還可分析得到其它相關(guān)結(jié)果:在無損系統(tǒng)中��,能量傳輸電容(CBLK2)上的穩(wěn)態(tài)電壓等于VOUT�����;流經(jīng)輸出電感(L1B)的直流電流值等于IOUT�;流經(jīng)地基準(zhǔn)電感(L1A)的直流電流值等于IOUT ×VOUT/VIN�����。該能量傳輸電容還能提供VIN至VOUT的隔直�����。當(dāng)存在輸出短路風(fēng)險(xiǎn)時(shí),此特性很有用��。

分析還顯示�,反相 SEPIC 中的輸出電流是連續(xù)的,對(duì)于給定輸出電容阻抗�����,會(huì)產(chǎn)生較低的峰峰值輸出電壓紋波����。這就允許使用較小、較便宜的輸出電容����;相比之下,在非連續(xù)輸出電流拓?fù)浣Y(jié)構(gòu)中�,為了達(dá)到同樣的紋波要求,需要使用較大且昂貴的電容��。

通常�,次級(jí)開關(guān)(QL1)是一個(gè)單向功率二極管,它會(huì)限制這種拓?fù)浣Y(jié)構(gòu)的峰值效率�。然而,利用ADI公司雙通道同步開關(guān)控制器ADP1877(見附錄)的一個(gè)通道��,并采用雙向MOSFET作為次級(jí)開關(guān)��,可以設(shè)計(jì)一個(gè)"完全同步配置"的反相SEPIC����。這樣,峰值效率將大大提高��,同時(shí)可以降低輸出電流大于 1 A的轉(zhuǎn)換器尺寸和成本�����。

圖 4 顯示完全同步反相SEPIC配置的功率級(jí)���,它利用ADP1877 實(shí)現(xiàn)���,只需要三個(gè)小型、廉價(jià)的額外器件(CBLK1��、DDRV和RDRV)�,其功耗可以忽略不計(jì)。

圖 4. 同步反相 SEPIC 的功率級(jí)�,利用 ADP1877 的通道 1 實(shí)現(xiàn)

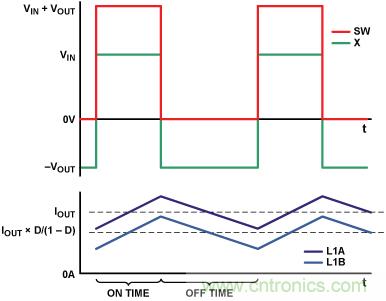

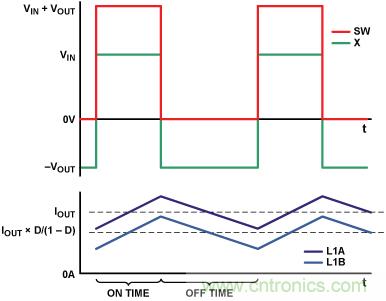

反相SEPIC的理想穩(wěn)態(tài)波形如圖 5 所示�。通道 1 開關(guān)節(jié)點(diǎn)SW1(見附錄圖A)在VIN + VOUT(導(dǎo)通時(shí)間內(nèi))和 0 V(關(guān)斷時(shí)間內(nèi))之間切換����。將電荷泵電容CBST連接到SW1,以便在導(dǎo)通時(shí)間內(nèi)將約為VIN + VOUT + 5 V的電壓施加于高端內(nèi)部驅(qū)動(dòng)器的自舉上電軌(BST1 引腳)和高端驅(qū)動(dòng)器的輸出(DH1 引腳)���,從而增強(qiáng)初級(jí)浮空N溝道MOSFET開關(guān)QH1����。箝位二極管DDRV確保穩(wěn)態(tài)輸出期間CBLK1上的電壓約為VOUT + VFWD(DDRV)��,該電壓參考ADP1877的DH1 引腳到QH1 柵極的電壓����。在關(guān)斷時(shí)間內(nèi),當(dāng)X節(jié)點(diǎn)電壓約為–VOUT時(shí)�����,CBLK1上的電壓阻止初級(jí)開關(guān)產(chǎn)生高于其閾值的柵極-源極電壓����。

圖 5. 同步反相 SEPIC 的理想波形(忽略死區(qū))

ADP1877 具有脈沖跳躍模式,使能時(shí)�,可以降低開關(guān)速率��,只向輸出端提供足以保持輸出電壓穩(wěn)定的能量�����,從而提高小負(fù)載時(shí)的效率,大大降低柵極電荷和開關(guān)損耗����。在同步反相 SEPIC 和同步降壓拓?fù)浣Y(jié)構(gòu)中均可以使能此模式。圖 4 所示 DC-DC 轉(zhuǎn)換電路只需要雙通道 ADP1877 的一個(gè)通道��,因此另一通道可以用于任一種拓?fù)浣Y(jié)構(gòu)����。

電感耦合和能量傳輸電容

圖 4 中,功率電感 L1A 和 L1B 顯示為彼此耦合�����。在這種拓?fù)浣Y(jié)構(gòu)中����,耦合電感的目的是減少輸出電壓和電感電流的紋波,并且提高最大可能閉環(huán)帶寬�����,下一部分將對(duì)此加以說明。

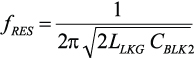

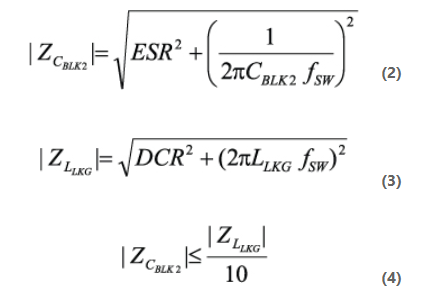

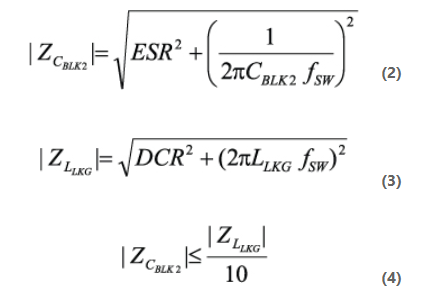

雖然這些電感互相耦合�,但并不希望耦合太緊,以至于將一個(gè)繞組的大量能量通過鐵芯傳輸至另一個(gè)繞組��。為了避免這一點(diǎn)��,必須求得耦合電感的泄漏電感(LLKG)�����,并選擇適當(dāng)?shù)哪芰總鬏旊娙?CBLK2)���,使得其復(fù)數(shù)阻抗的幅值為泄漏電感與單個(gè)繞組電阻(DCR)的復(fù)串聯(lián)阻抗的 1/10���,如方程式 2、3��、4 所示�����。按照這一關(guān)系設(shè)計(jì)電路,可使耦合鐵芯所傳輸?shù)哪芰拷抵磷畹?。泄漏電感可以根?jù)耦合電感數(shù)據(jù)手冊中提供的耦合系數(shù)計(jì)算。

匝數(shù)比最好為 1:1��,因?yàn)閷?duì)于給定水平的輸出電壓紋波���,此時(shí)各繞組只需要分立電感所需電感的一半1�??梢允褂?1:1 以外的匝數(shù)比����,但其結(jié)果將無法用本文中的方程式準(zhǔn)確描述。

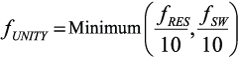

小信號(hào)分析和環(huán)路補(bǔ)償

反相 SEPIC 轉(zhuǎn)換器的完整小信號(hào)分析超出了本文的范圍���,不過���,如果遵照下述原則,完整分析將更具學(xué)術(shù)意義�����。

首先必須計(jì)算諧振頻率(fRES)時(shí)的許多復(fù)數(shù)阻抗交互����,以便求得目標(biāo)交越頻率的上限����。當(dāng)電感解耦時(shí)��,此頻率降低�,導(dǎo)致最大可能閉環(huán)帶寬顯著降低。

(5)

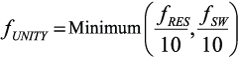

在此頻率時(shí)�,可能有 300°或更大的"高Q"相位遲滯。為了避免轉(zhuǎn)換器在整個(gè)負(fù)載范圍內(nèi)相位裕量偏小的問題����,目標(biāo)交越頻率(fUNITY)應(yīng)為fRES的 1/10。此諧振的阻尼主要取決于輸出負(fù)載電阻和耦合電感的直流電阻�。在較小程度上,阻尼還取決于能量傳輸電容的等效串聯(lián)電阻(ESR)和功率MOSFET(QHl和QL1)的導(dǎo)通電阻��。因此���,當(dāng)輸出負(fù)載電阻改變時(shí)���,閉環(huán)傳遞函數(shù)的特征在該頻率時(shí)發(fā)生明顯變化也不足為奇。

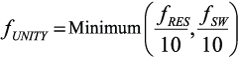

耦合系數(shù)通常不是一個(gè)能夠精確控制的參數(shù)��,因此應(yīng)將目標(biāo)交越頻率設(shè)置為比fRES低 10 倍的值(假設(shè)fRES小于開關(guān)頻率fSW)。當(dāng)fUNITY設(shè)置適當(dāng)時(shí)���,可以使用標(biāo)準(zhǔn)"II型"補(bǔ)償——兩個(gè)極點(diǎn)和一個(gè)零點(diǎn)���。

(6)

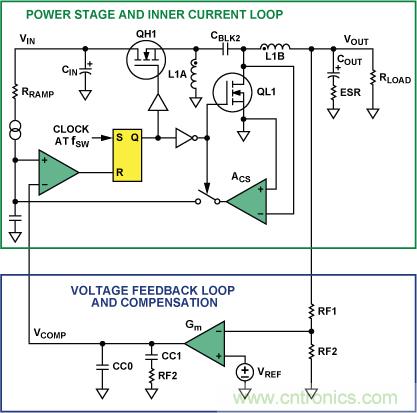

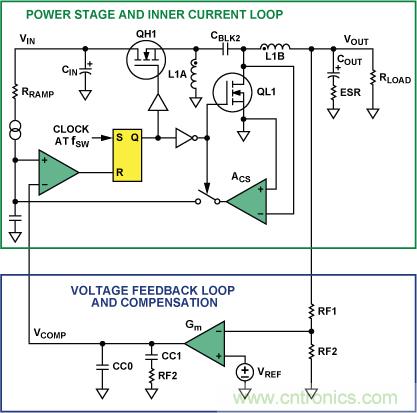

圖6 顯示同步反相SEPIC 降壓/升壓拓?fù)浣Y(jié)構(gòu)中ADP1877反饋環(huán)路的等效電路。上框包含功率級(jí)和電流環(huán)路����,下框包含電壓反饋環(huán)路和補(bǔ)償電路。

圖 6. 同步反相 SEPIC 拓?fù)浣Y(jié)構(gòu)中 ADP1877 具有內(nèi)部電流檢測 I環(huán)路的功率級(jí)和補(bǔ)償方案

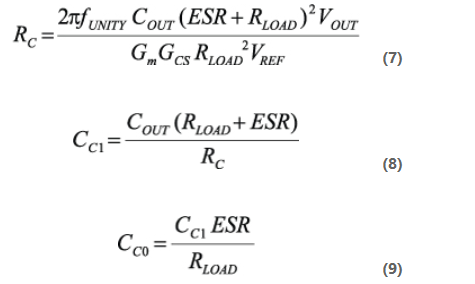

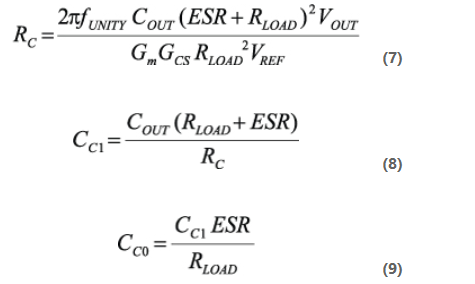

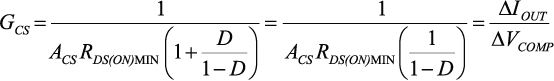

下框中的補(bǔ)償元件值可以通過下式計(jì)算:

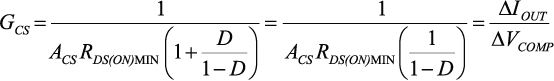

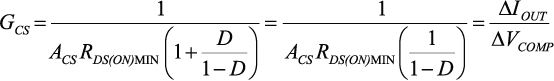

轉(zhuǎn)換器的跨導(dǎo)GCS利用下式計(jì)算:

(10)

COUT是轉(zhuǎn)換器的輸出電容����。ESR是該輸出電容的等效串聯(lián)電阻����。RLOAD是最小輸出負(fù)載電阻。ACS是電流檢測增益����,對(duì)于ADP1877,它可以在 3 V/V至 24 V/V范圍內(nèi)以離散步進(jìn)選擇�����。Gm是誤差放大器的跨導(dǎo),ADP1877 為 550 μs�。VREF是與誤差放大器的正輸入端相連的基準(zhǔn)電壓,ADP1877 為 0.6 V�。

GCS是與頻率無關(guān)的增益項(xiàng),隨增強(qiáng)后的次級(jí)開關(guān)電阻RDS(ON)而變化����。最高交越頻率預(yù)期出現(xiàn)在此電阻和占空比D最低時(shí)。

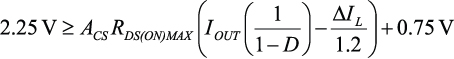

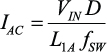

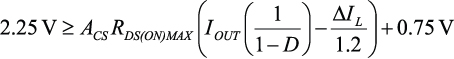

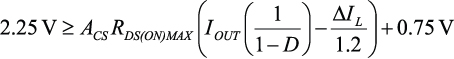

為確保在最大輸出電流時(shí)不會(huì)達(dá)到補(bǔ)償箝位電壓��,所選的電流檢測增益(ACS)最高值應(yīng)滿足以下條件:

(11)

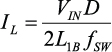

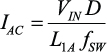

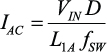

其中?IL為峰峰值電感紋波電流��。

(12)

如果斜率補(bǔ)償過多�����,此處的方程式精確度將會(huì)下降:直流增益將降低����,輸出濾波器將引起主極點(diǎn)的頻率位置提高。

斜率補(bǔ)償

對(duì)于利用ADP1877 實(shí)現(xiàn)的同步反相SEPIC����,必須考慮電流模式控制器2中的次諧波振蕩現(xiàn)象。

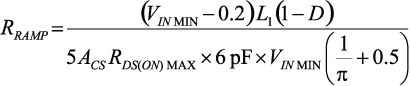

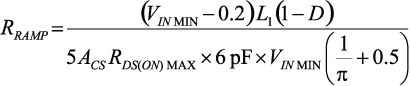

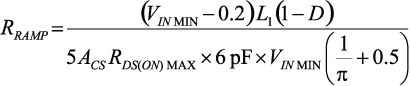

按照下式設(shè)置RRAMP����,可以將采樣極點(diǎn)的品質(zhì)因素設(shè)為 1����,從而防止發(fā)生次諧波振蕩3(假設(shè)fUNITY設(shè)置適當(dāng))��。

(13)

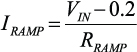

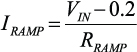

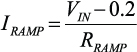

值得注意的是����,隨著增強(qiáng)后的次級(jí)開關(guān)電阻RDS(ON)降低,采樣極點(diǎn)的Q也會(huì)下降���。如果這一因素與其它相關(guān)容差一起導(dǎo)致Q小于0.25���,則應(yīng)進(jìn)行仿真,確保在考慮容差的情況下���,轉(zhuǎn)換器不會(huì)有過多斜率補(bǔ)償,并且不是太偏向于電壓模式�。RRAMP的值必須使得ADP1877 RAMP引腳的電流在 6 μA至 200 μA范圍內(nèi),其計(jì)算公式 14 如下:

(14)

功率器件應(yīng)力

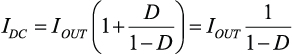

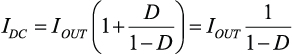

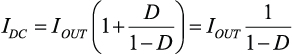

從圖 2 和圖 3 的電流流向圖可以看出�,功率 MOSFET 在接通后要承載電感電流總和。因此��,流經(jīng)兩個(gè)開關(guān)的電流直流分量為:

(15)

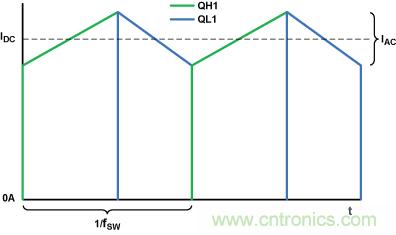

如果電感的耦合比為 1:1,則流經(jīng)兩個(gè)開關(guān)的電流交流分量為:

(16)

知道這些值后����,可以很快算出流經(jīng)各開關(guān)的電流均方根值。這些值與所選MOSFET的RDS(ON)MAX共同確保MOSFET具有熱穩(wěn)定性���,同時(shí)功耗足夠低����,以滿足效率要求�。

圖 7. 同步反相 SEPIC 的理想電流波形(忽略死區(qū))

精確計(jì)算初級(jí)開關(guān)的開關(guān)損耗超出了本文的范圍,但應(yīng)注意���,從高阻態(tài)變?yōu)榈妥钁B(tài)時(shí)���,MOSFET上的電壓擺輻約為VIN + VOUT至 0V,流經(jīng)開關(guān)的電流擺輻為 0 A至IOUT[1/(1–D)]���。由于擺幅如此之高���,開關(guān)損耗可能是主要損耗,這是挑選MOSFET時(shí)應(yīng)注意的一點(diǎn)����;對(duì)于MOSFET��,反向傳輸電容(CRSS)與RDS(ON)成反比���。

初級(jí)開關(guān)和次級(jí)開關(guān)的漏極-源極擊穿電壓(BVDSS)均須大于輸入電壓與輸出電壓之和(見圖 5)。

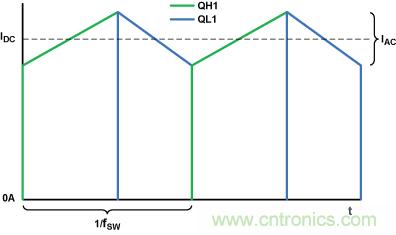

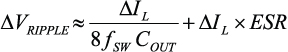

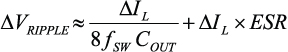

峰峰值輸出電壓紋波(?VRIPPLE)可通過下式近似計(jì)算:

(17)

流經(jīng)輸出電容的電流均方根值(I rms COUT)為:

(18)

方程式 12 所表示的峰峰值電感電流(?IL)取決于輸入電壓����,因此必須確保當(dāng)此參數(shù)改變時(shí),輸出電壓紋波不會(huì)超過規(guī)定值����,并且流經(jīng)輸出電容的均方根電流不會(huì)超過其額定值。

對(duì)于利用ADP1877 實(shí)現(xiàn)的同步反向SEPIC�,輸入電壓與輸出電壓之和不得超過 14.5 V,因?yàn)殡姾杀秒娙菖c開關(guān)節(jié)點(diǎn)相連�����,當(dāng)初級(jí)開關(guān)接通時(shí)����,其電壓達(dá)到VIN + VOUT�。

實(shí)驗(yàn)室結(jié)果

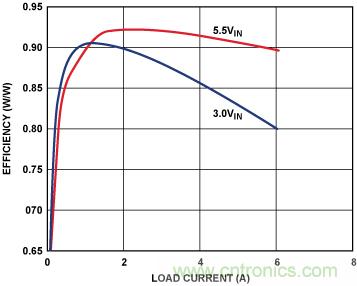

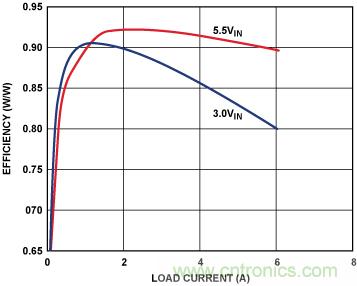

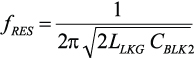

圖 8 顯示 5 V 輸出���、3 V 和 5.5 V 輸入時(shí)同步反向 SEPIC 的功效與負(fù)載電流的關(guān)系。對(duì)于需要在 3.3 V 和 5.0 V 輸入軌之間切換的應(yīng)用�����,或者當(dāng)實(shí)時(shí)調(diào)整輸入電壓以優(yōu)化系統(tǒng)效率時(shí)���,這是常見情況�����。采用 1 A 至 2 A 負(fù)載時(shí)����,無論輸入電壓高于或低于輸出電壓����,轉(zhuǎn)換器的效率均超過 90%。

圖 8. 效率與負(fù)載電流的關(guān)系

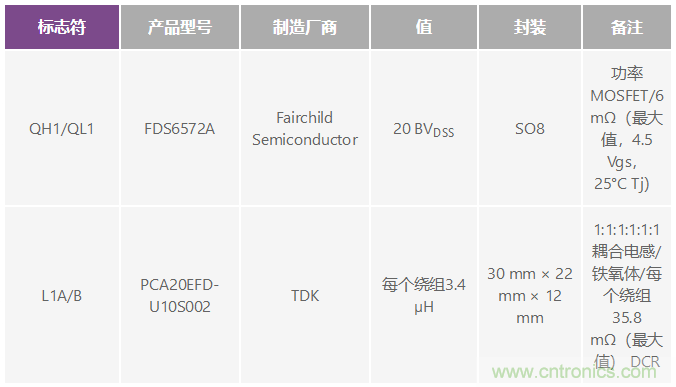

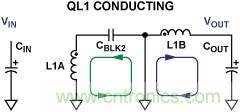

與圖 8 相關(guān)的功率器件材料清單見表 1�����,其中僅采用常見的現(xiàn)成器件��。一項(xiàng)具可比性的異步設(shè)計(jì)采用一個(gè)具有低正向壓降的業(yè)界領(lǐng)先肖特基二極管代替 QL1,在以上兩種輸入電壓下�,其滿載時(shí)的效率低近 10%。此外���,異步設(shè)計(jì)尺寸更大�����、成本更高���,而且可能需要昂貴的散熱器。

表 1. 功率器件

結(jié)束語

許多市場對(duì)輸出電壓高于或低于輸入電壓(升壓/降壓)的高效率同相轉(zhuǎn)換器的需求都在不斷增長����。ADI 公司的雙通道同步開關(guān)控制器ADP1877允許用低損耗MOSFET代替常用于功率級(jí)的高損耗功率二極管,從而提高效率����,降低成本,縮小電路尺寸����,使系統(tǒng)達(dá)到苛刻的能耗要求。只要遵循幾項(xiàng)原則就能快速算出可靠補(bǔ)償所需的元件值,并且利用常見的現(xiàn)成器件便可實(shí)現(xiàn)高效率�。

參考電路

Barrow, Jeff. "Reducing Ground Bounce in DC-to-DC Converters—Some Grounding Essentials." Analog Dialogue. 41-2, pp. 2-7. 2007.

1?uk, Slobodan and R.D. Middlebrook. "Coupled-Inductor and Other Extensions of a New Optimum Topology Switching DC-DC Converter." Advances in Switched-Mode Power Conversion. Volumes I & II. Irvine, CA: TESLAco. 1983.

2Erickson, Robert and Dragan Maksimovi?. Fundamentals of Power Electronics. Chapter 12, Section 1. Norwell, MA: Kluwer Academic Publishers. 2001.

3Ridley, Raymond. "A New Small-Signal Model for Current-Mode Control." PhD Dissertation, Virginia Polytechnic Institute and State University. November 1990.

附錄

ADP1877是一款Flex-ModeTM(ADI公司專有架構(gòu))雙通道開關(guān) 控制器��,如圖A所示���,其集成驅(qū)動(dòng)器可驅(qū)動(dòng)N溝道同步功率 MOSFET�。兩路PWM輸出相移 180°�,可降低輸入均方根電流, 從而使所需的輸入電容最小�����。

圖 A. ADP1877 示意框圖��。僅顯示通道 1��;通道 2 與之完全相同�����,帶后綴 2��。

ADP1877 內(nèi)置升壓二極管����,因而整體元件數(shù)量和系統(tǒng)成本得以 減少���。在小負(fù)載時(shí),可以將它設(shè)置為高效率脈沖跳躍工作模式�, 也可以是 PWM 連續(xù)傳導(dǎo)工作模式。

ADP1877 內(nèi)置外部可調(diào)軟啟動(dòng)功能�����、輸出過壓保護(hù)��、外部可調(diào) 電流限制��、電源良好指示���,并提供 200 kHz 至 1.5 MHz 的可編程 振蕩器頻率�����。工作溫度范圍為–40°C 至+85°C 時(shí)�����,輸出電壓精 度為±0.85%���;工作溫度范圍為–40°C 至+125°C 結(jié)溫范圍時(shí)��, 輸出電壓精度為±1.5%�����。其工作電源電壓為 2.75 V 至 14.5 V, 采用 32 引腳����、5 mm × 5 mm LFCSP 封裝。

推薦閱讀:

(5)

(5) (6)

(6)

(10)

(10) (11)

(11) (13)

(13) (14)

(14) (15)

(15) (16)

(16)

(17)

(17) (18)

(18)

(5)

(5) (6)

(6)

(10)

(10) (11)

(11) (13)

(13) (14)

(14) (15)

(15) (16)

(16)

(17)

(17) (18)

(18)