【導(dǎo)讀】現(xiàn)代SAR和∑-Δ型模數(shù)轉(zhuǎn)換器(ADC)的主要優(yōu)勢(shì)之一是在設(shè)計(jì)中考慮了易用性����,這是針對(duì)前幾代設(shè)計(jì)的補(bǔ)充。不僅簡化了系統(tǒng)設(shè)計(jì)人員的工作��,而且在許多情況下�����,允許對(duì)多代各種應(yīng)用重復(fù)使用單個(gè)參考設(shè)計(jì)����。在很多情況下,您可以構(gòu)建一個(gè)參考設(shè)計(jì)長時(shí)間用于不同的應(yīng)用���。精密測(cè)量系統(tǒng)的硬件保持不變��,而軟件實(shí)現(xiàn)可適應(yīng)不同系統(tǒng)的需要���。這就是可重用使用的美妙之處,但實(shí)際生活中沒有萬事如意—有利也有弊�。

多個(gè)應(yīng)用采用單一設(shè)的主要缺點(diǎn)是,您放棄了實(shí)現(xiàn)dc��、地震、音頻和更高帶寬應(yīng) 用的絕對(duì)最高可能性能所需的自定義和優(yōu)化��。在急于重用和完 成設(shè)計(jì)的過程中����,往往會(huì)犧牲精確性能。其容易忽略和忽視 的一個(gè)主要方面是時(shí)鐘���。在本文中���,我們將討論時(shí)鐘的重要性, 并為正確設(shè)計(jì)高性能轉(zhuǎn)換器提供指導(dǎo)���。

ADC基礎(chǔ)知識(shí)

抖動(dòng)和信噪比之間的關(guān)系

在查閱現(xiàn)有文獻(xiàn)時(shí)�����,我們看到了有關(guān)ADC性能依賴于抖動(dòng)參數(shù)的 大量描述���,并且通常此類標(biāo)題會(huì)包含“高速”一詞,這不無道 理��。1為了考察抖動(dòng)和信噪比(SNR)之間的關(guān)系,首先來看SNR數(shù) 值和rms抖動(dòng)之間的關(guān)系����。

如果抖動(dòng)是系統(tǒng)中的主要噪聲源,則此關(guān)系簡化為:

如果有不同的噪聲源���,則需要使用等式2來計(jì)算組合SNR:

其中:

ev 是簡化的電壓噪聲r(shí)ms

δtRMS 是以各種來源的rms總和估算的總rms抖動(dòng):

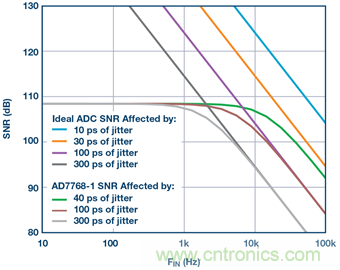

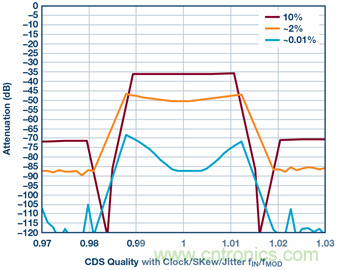

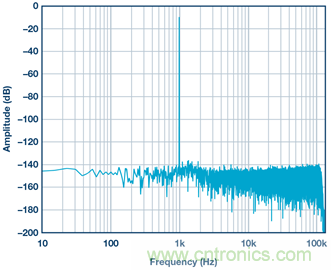

求和對(duì)不相關(guān)噪聲源有效��。利用等式2,可得到基于熱噪聲(e2v) 和抖動(dòng)噪聲的SNR����。抖動(dòng)對(duì)SNR的影響取決于輸入頻(fIN)。這表 示在較高的頻率下���,SNR主要由抖動(dòng)定義�����。圖1所示是根據(jù)等式1和等式2得到的受抖動(dòng)影響的理想和實(shí)際ADC的曲線���。圖1中的曲線在高速ADC數(shù)據(jù)手冊(cè)中很常見,但通常在MHz范圍開始��。對(duì)于精密ADC��,我們將進(jìn)一步在kHz范圍內(nèi)展示相同的依賴關(guān)系。我們使SNR超過108dB(參見圖1)��,精密ADC現(xiàn)在能夠做到這一點(diǎn)����。這正是AD7768-1的用武之地。

不同抖動(dòng)水平下 SNR 和 fIN的關(guān)系��。

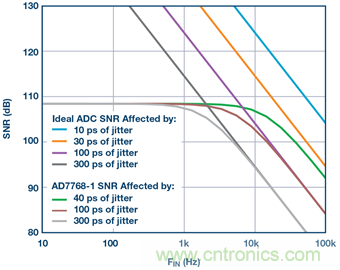

查看圖1中的曲線��,可以看到僅當(dāng)σtRMS超過300ps時(shí)��,AD7768-1轉(zhuǎn)換1kHz信號(hào)(灰色線)才會(huì)受到時(shí)鐘抖動(dòng)的影響��。我們可以調(diào)整變量并顯示特定ENOB和fIN的抖動(dòng)要求:

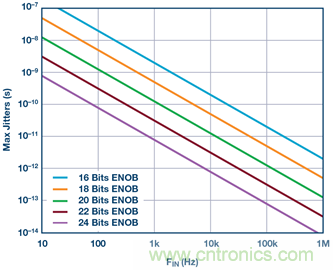

圖2. 在轉(zhuǎn)換器不同ENOB下最大允許抖動(dòng)和fIN的關(guān)系�。

目前高精度轉(zhuǎn)換器的目標(biāo)抖動(dòng)使得設(shè)計(jì)人員不能選擇使用通用振蕩器(如555定時(shí)器振蕩器)或許多微控制器或基于FPGA的時(shí)鐘發(fā)生器。我們只能選擇晶體(XTAL)和鎖相環(huán)(PLL)振蕩器���。新型 MEMS振蕩器技術(shù)也會(huì)適用�����。

過采樣技術(shù)在這里有用嗎�����?

在等式1和等式2中可以觀察到重要的一點(diǎn)����,抖動(dòng)對(duì)采樣頻率沒有明顯的依賴關(guān)系。這意味著���,很難通過過采樣技術(shù)(平面或噪聲整形)來減少抖動(dòng)的影響�����。過采樣在高精度系統(tǒng)中很常見, 但在對(duì)抗抖動(dòng)噪聲方面幾乎沒有什么作用��。與采樣頻率的關(guān)系 見等式4

其中:

L(f)是相位噪聲頻譜單邊帶(SSB)密度函數(shù)

fmin和fmax是與特定測(cè)量相關(guān)的頻率范圍�。

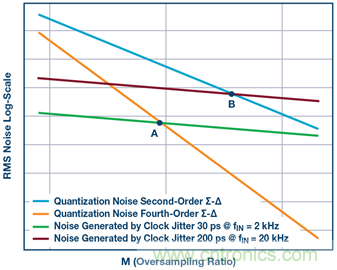

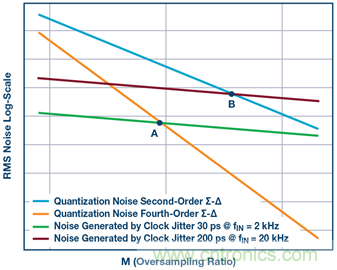

一般來說,增加fS對(duì)改善抖動(dòng)影響用處不大�。22理論上講,ADC的 過采樣率會(huì)減少一些寬帶抖動(dòng)影響����。3在量化噪聲和熱噪聲方面,噪聲整形是抑制目標(biāo)頻段噪聲的一種非常有效的方法���。如等式7所示���,與噪聲抖動(dòng)抑制相比�����,增加過采樣率能夠更快地抵制量化噪聲(等式5)��。這使得抖動(dòng)在利用噪聲整形的過采樣結(jié)構(gòu)中更加突出����。在奈奎斯特轉(zhuǎn)換器中���,這可能沒有那么嚴(yán)重�����。圖3以二階∑-ΔADC和新四階∑-ΔADC為例說明了這一現(xiàn)象����。

使用基本誤差為Δ的N階整形器在過采樣率M下整形的量化噪聲之間的關(guān)系:

過采樣率M和抖動(dòng)量之間的關(guān)系:

等式7顯示二階噪聲整形(N = 2)�。應(yīng)將注意力放M上,M現(xiàn)在以5次方變化��。

圖3.過采樣將量化噪聲降至低于抖動(dòng)導(dǎo)致的噪聲限值。A 點(diǎn)顯示四階∑-Δ ADC 要求時(shí)鐘抖動(dòng)低于 30 ps���。B點(diǎn)說明采用較早技術(shù)的二階整形器進(jìn)行200 kHz轉(zhuǎn)換時(shí)不受高達(dá) 200 ps 抖動(dòng)水平影響�。

不同代的轉(zhuǎn)換器會(huì)看到一些共同的關(guān)系特性����。一階噪聲整形器 隱藏抖動(dòng)的時(shí)間最長,從而將三次關(guān)系推進(jìn)到~1/M3���,而四階∑-Δ將獲得~1/M9的關(guān)系���。抖動(dòng)最多會(huì)降低1/M,,而這通常假定存在較 強(qiáng)的寬帶頻率分量��,而非關(guān)系1/(fN)���。

信號(hào)振幅會(huì)改變現(xiàn)狀嗎?

等式2顯示分子和分母中均有振幅�����,使振幅和SNR值之間無法實(shí) 現(xiàn)良好的平衡�。在衰減信號(hào)中��,除了抖動(dòng)外�,熱噪聲開始限制 動(dòng)態(tài)范圍���,從而使SNR變差����。因此��,我們可以看到����,如果通過 新的精密ADC來實(shí)現(xiàn)足夠低的噪聲,精密ADC將在幾乎所有應(yīng)用 (dc/地震應(yīng)用除外)中受到抖動(dòng)限制�。

時(shí)鐘抖動(dòng)也會(huì)有頻譜

在前面的介紹中,我們確立了信號(hào)���、總電壓噪聲和時(shí)鐘抖動(dòng)rms之間關(guān)系����。SNR通過非常簡單的等式2將這三者聯(lián)系在一起���。SNR是用于比較電路設(shè)計(jì)的一個(gè)很好的基準(zhǔn)����,但在實(shí)際應(yīng)用中未必可行。在很多應(yīng)用中���,專門針對(duì)SNR的設(shè)計(jì)不夠理想���。因此,無雜散動(dòng)態(tài)范圍(SFDR)成為設(shè)計(jì)目標(biāo)���。在新的高精度系統(tǒng)中��,可實(shí)現(xiàn)140dB甚至150 dB的SFDR����。

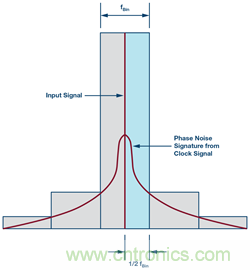

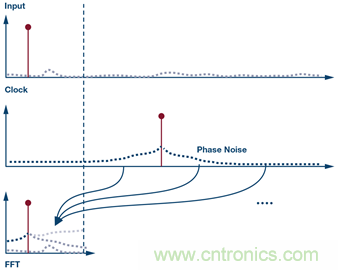

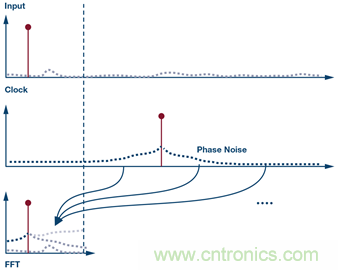

由時(shí)鐘源導(dǎo)致信號(hào)失真的過程可以通過混合二者來檢查����。可采用 FM調(diào)制理論分析頻域��。3得到的快速傅立葉變換(FFT)頻譜是時(shí)鐘源頻譜與輸入信號(hào)頻譜混合的產(chǎn)物�����。為查看我們的ADC如何受此影響�����,我們引入了相位噪聲����。抖動(dòng)和相位噪聲均描述相同的現(xiàn)象,但將根據(jù)應(yīng)用首選一種���。我們已經(jīng)展示了如何在等式3中將 相位噪聲轉(zhuǎn)換成抖動(dòng)�����。在積分過程中���,頻譜的細(xì)微差別將丟失。

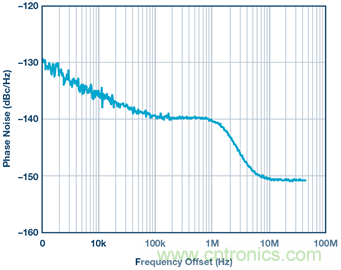

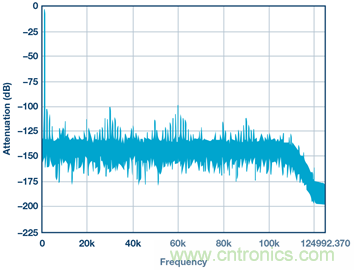

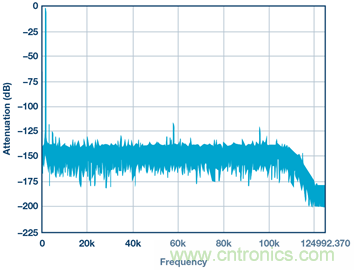

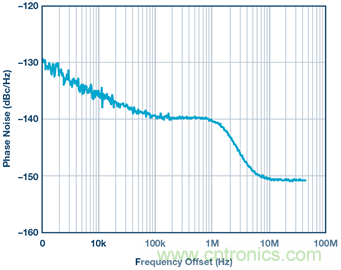

圖4. 100 MHz/33.33MHz 時(shí)鐘發(fā)生器 AD9573的相位噪聲密度圖��。

相位噪聲密度圖通常與時(shí)鐘源設(shè)備和PLL規(guī)范一起提供���。對(duì)于較低頻率源�����,圖4所示的曲線變得更少見����,這些頻率源用于當(dāng)前的過采樣轉(zhuǎn)換器,但報(bào)告總抖動(dòng)值(rms或峰值)�。

通過斬波方案,可以強(qiáng)制電阻和晶體管元件在直流附近表現(xiàn)出 相當(dāng)平坦的噪聲特性�����。沒有等效的時(shí)鐘斬波電路可用�。

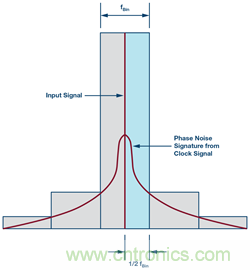

在轉(zhuǎn)換高幅度AIN信號(hào)時(shí),得到的FFT變?yōu)镕M調(diào)制頻譜�����,其中AIN充當(dāng)載波���,時(shí)鐘邊帶與信號(hào)等效����。請(qǐng)注意�����,相位噪聲在FFT中不會(huì) 受到頻帶限制��,噪聲在頻帶內(nèi)表現(xiàn)為多個(gè)鏡像混疊片段(參見 圖5)�����。

在精密ADC中���,通?�?梢砸蕾囅辔辉肼暤淖匀凰p特性而不提供任何時(shí)鐘抗混疊濾波器��。通過向時(shí)鐘源添加濾波����,可以減少一些抖動(dòng)—例如����,在時(shí)鐘路徑中使用調(diào)諧變壓器來表現(xiàn)出理想的頻率響應(yīng)。求積分頻率的積分上限(等式3)并不容易確定��。精密ADC數(shù)據(jù)手冊(cè)未對(duì)此提供太多建議��。在這些情況下,對(duì)時(shí)鐘CMOS輸入進(jìn)行了工程假設(shè)�����。

精密ADC中更常見的問題發(fā)生在fIN頻率附近���,其中1/(fN)形狀的相 位噪聲將使SFDR特性更差����。大的AIN信號(hào)將充當(dāng)阻塞器��,這是一個(gè) 在無線電接收器中更常用的術(shù)語���,這里也適用��。

旨在記錄具有非常長捕獲時(shí)間的高精度頻譜時(shí)����,由于時(shí)鐘相位噪聲頻譜密度的性質(zhì)���,時(shí)間將受到很大影響�。SNR和FFT圖可通過縮短捕獲時(shí)間(更寬的頻率帶)來改進(jìn)���。對(duì)于給定的FFT捕獲��, rms抖動(dòng)應(yīng)計(jì)為?頻帶的集成相位噪聲����。查看圖5�,可以很明顯地 看到這一點(diǎn)。

圖5.近載波相位噪聲確定主頻帶周圍的 FFT頻帶的幅度�����。

雖然這一技巧可以明顯改善FFT和SNR曲線���,但對(duì)觀察阻塞器附近 的信號(hào)沒有任何幫助���。FM調(diào)制等式的一個(gè)重要概括和簡化是邊 緣高度與下面成正比:

延長單次FFT的積分時(shí)間是一項(xiàng)挑戰(zhàn),需要進(jìn)一步捕獲更多和更 突出的相位噪聲部分�����。我們需要考慮組合更長時(shí)間捕獲的替代 方式來改進(jìn)這一點(diǎn)���。

圖 6. 相位噪聲向下混疊到基帶���。

出于實(shí)際考慮��,應(yīng)在fBIN/2偏移頻率下在單個(gè)點(diǎn)比較SSB曲線�,以 選取更好的源�,獲得干凈的近載波頻譜和SFDR。如果比較源以 實(shí)現(xiàn)更好的SNR���,則需要從fBIN/2到超過fS(抖動(dòng)別名)的3倍執(zhí)行 等式3中的積分���。

∑-Δ型調(diào)制器對(duì)時(shí)鐘的敏感性

無論何種架構(gòu)和技術(shù),前面所述都適用于任何ADC�����。下面將討論特定技術(shù)帶來的挑戰(zhàn)���。抖動(dòng)依賴性最突出的示例之一是∑-Δ型ADC����。離散時(shí)間和連續(xù)時(shí)間調(diào)制器之間的差別在抗抖動(dòng)性方面有 很大差別�����。

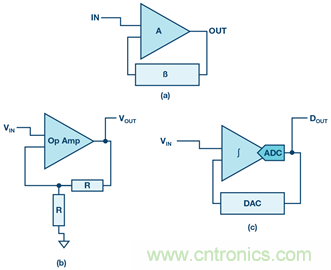

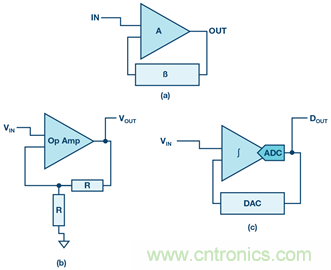

連續(xù)時(shí)間和離散時(shí)間∑-Δ型ADC不僅受到與采樣相關(guān)的抖動(dòng)的影響,其反饋環(huán)路也可能受到抖動(dòng)的嚴(yán)重干擾��。離散時(shí)間和連續(xù)時(shí)間調(diào)制器中DAC元件的線性度是實(shí)現(xiàn)高性能的關(guān)鍵��。通過與運(yùn)算放大器(opamp)并聯(lián)可以直觀地了解DAC的重要性���。如果設(shè)計(jì)一個(gè)增益等于2的電壓放大器���,那么電路設(shè)計(jì)人員通常首先會(huì)考慮使用一個(gè)運(yùn)算放大器和兩個(gè)電阻���。如果不是極端外部環(huán)境����,圖7a中所示的電路就符合要求����。在大多數(shù)情況下,電路設(shè)計(jì)人員不需要了解運(yùn)算放大器就能獲得很好的性能���。設(shè)計(jì)人員必須選擇匹配良好且精度足以獲得正確增益的電阻���。為了減少噪聲����,電阻必須很小�����。在熱性能方面需要考慮熱系數(shù)匹配���。請(qǐng)注意���,這些依賴因素都不是由運(yùn)算放大器決定的。對(duì)于這種電路操作���,運(yùn)算放大器不理想的影響并不重要��。沒錯(cuò)����,輸入電流或容性負(fù)載可能影響大�。需要檢查壓擺能力,因?yàn)槿绻麕挷皇芟拗?���,可能要考慮噪聲影響���。但是只有在選擇正確電阻而未影響性能的情況下,才能解決這些問題�����。在∑-Δ型AC中�,反饋比兩個(gè)電阻更復(fù)雜—在這些電路中,我們使用DAC代替電阻執(zhí)行相應(yīng)功能����。當(dāng)電路的其余部分以類似于運(yùn)算放大器電路的方式獲得環(huán)路增益,DAC做法中的缺陷就會(huì)很不利����。

圖 7. 運(yùn)算放大器與 ∑-Δ 型 ADC比較���。

ADC采用元件混搭(shuffling)或校準(zhǔn)���,這提供了一種處理DAC元件不匹配的方法。這些混搭或校準(zhǔn)會(huì)將錯(cuò)誤轉(zhuǎn)移到高頻率����,但也會(huì)使用更多的定時(shí)事件��,并可能增加與抖動(dòng)相關(guān)的性能下降���。最終造成噪底受到抖動(dòng)影響污染的情況,從而降低噪聲整形的有效性�。因?yàn)檎{(diào)制器可以采用不同的DAC方案以及它們的混合,例如歸零和半歸零��。深入研究這些方案進(jìn)行分析和數(shù)值模擬超出了 本文的范圍�����。

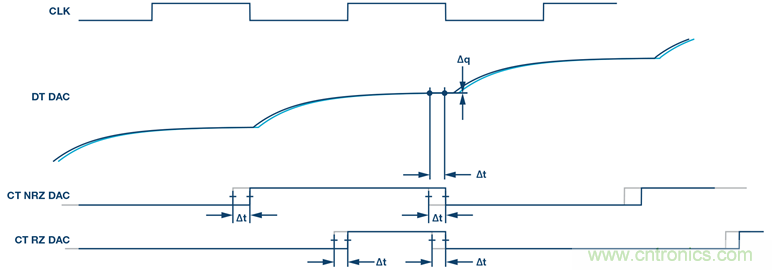

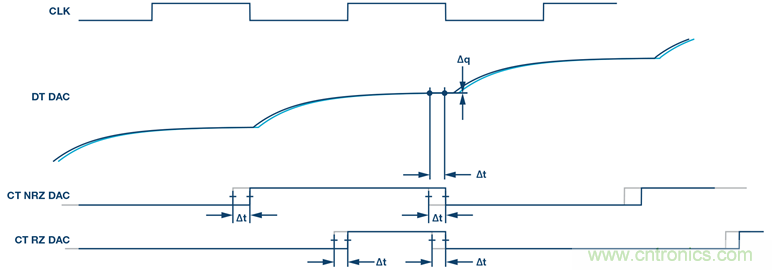

關(guān)于本文中的抖動(dòng)�����,我們將通過圖示形式簡化���。由于ADC環(huán)路內(nèi)存在抖動(dòng)依賴性問題�����,一些新型設(shè)計(jì)將在芯片上提供具有適當(dāng)相位噪聲量的倍頻器�����。雖然這會(huì)省去系統(tǒng)設(shè)計(jì)人員的大部分工作���,但請(qǐng)注意���,倍頻器仍然依賴于良好的外部時(shí)鐘和低噪聲電源。在這些系統(tǒng)中����,應(yīng)考慮查看PLL文獻(xiàn),了解對(duì)觀察到的相位噪聲的潛在威脅�����。圖8顯示不同DAC的抗抖動(dòng)性能��,顯示離散時(shí) 間DAC運(yùn)行時(shí)影響極小�。

圖 8. 離散時(shí)間 DAC 在某種程度上抗抖動(dòng)����,而在連續(xù)時(shí)間DAC中,窄脈沖將對(duì)抖動(dòng)性能具有顯著的影響 ��。

現(xiàn)代連續(xù)時(shí)間∑-Δ型設(shè)計(jì)包括板上PLL�����。由于在與無源元件一致的情況下仔細(xì)調(diào)整時(shí)序,因此它們不提供各種時(shí)鐘速度�����?��?刹捎媚撤N人工方式擴(kuò)大ADC轉(zhuǎn)換率的選擇范圍�,這種方法采用采樣率轉(zhuǎn)換的方式�����。采樣率轉(zhuǎn)換雖然具有數(shù)字電路的優(yōu)點(diǎn)���,但會(huì)增加功耗��,不過這些代價(jià)仍使它值得成為高度調(diào)諧的模擬電路的替代方案���。ADI公司的許多ADC都提供采樣率轉(zhuǎn)換選項(xiàng)。

采用開關(guān)電容濾波器的架構(gòu)

精確定時(shí)可能影響性能的另一個(gè)特定領(lǐng)域是開關(guān)電容濾波�����。設(shè)計(jì)精密ADC時(shí),需要確保將所有干擾信號(hào)排除或充分衰減����。ADC可能要提供特定嵌入式模擬和數(shù)字濾波。ADC的數(shù)字濾波具有很 強(qiáng)的抗抖動(dòng)能力����,而任何形式的時(shí)鐘模擬濾波都會(huì)受抖動(dòng)影響。

當(dāng)精密轉(zhuǎn)換器采用更先進(jìn)的前端開關(guān)時(shí)�����,這一點(diǎn)尤為重要�����。雖 然開關(guān)電容濾波器從理論上可能是有優(yōu)點(diǎn)����,但我們只能參考摘 要進(jìn)一步研究和分析。3

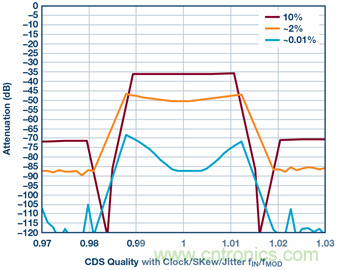

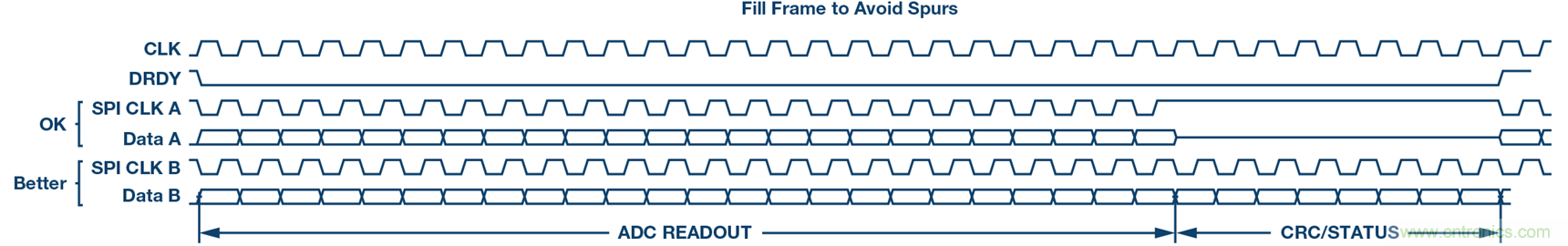

轉(zhuǎn)換器中常見的方案之一是相關(guān)雙采樣(CDS)����。參見圖9,了解CDS抑制質(zhì)量的性能如何隨時(shí)鐘以三種不同的質(zhì)量水平而變化���。圖中顯示阻帶附近的信號(hào)�����。顯示了在x軸上以1為中心的開關(guān)電容濾波器���。圖的中心未被數(shù)字濾波抑制,并且依賴于模擬開關(guān)電容濾波器����。需要優(yōu)質(zhì)時(shí)鐘來保持良好的抑制水平。即使測(cè)量dc信號(hào)�����,抖動(dòng)也會(huì)通過向下混疊干擾信號(hào)來影響噪聲性能���,這些信號(hào)本應(yīng)由硅片上的開關(guān)電容濾波器濾除��。數(shù)據(jù)手冊(cè)中可能沒有明確提到是否存在板載開關(guān)電容濾波器���。

圖 9. 開關(guān)電容濾波性能與時(shí)鐘質(zhì)量—傳號(hào)空號(hào)比。

實(shí)用指南、問題根源和常見猜測(cè)

至此�����,我們已經(jīng)展示了時(shí)鐘會(huì)給您帶來問題的幾種情況����,現(xiàn)在 來看看能夠幫助您實(shí)現(xiàn)最大限度減少抖動(dòng)量系統(tǒng)的技術(shù)。

時(shí)鐘信號(hào)反射

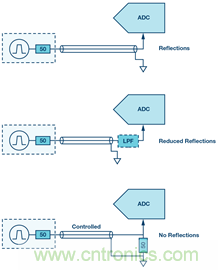

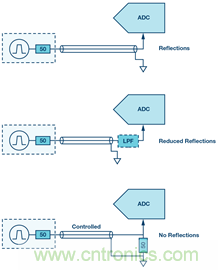

高質(zhì)量時(shí)鐘源具有非??焖俚纳仙拖陆禃r(shí)間。其優(yōu)勢(shì)是在轉(zhuǎn)換時(shí)減少抖動(dòng)噪聲��。遺憾的是���,由于陡峭邊沿的好處�����,對(duì)正確的路由和端接提出了相當(dāng)嚴(yán)格的要求�。如果時(shí)鐘線未正確端接��,該線路將受到添加到原始時(shí)鐘信號(hào)的反射波的影響����。此過程非常具有破壞性���,且相關(guān)的抖動(dòng)水平可輕松占據(jù)數(shù)百皮秒�。在極端情況下,時(shí)鐘接收器能夠看到可能導(dǎo)致鎖定電路的額外邊沿�����。

圖 10. 有關(guān)時(shí)鐘的 不佳�����、較佳���、最佳電路設(shè)計(jì)(按降序排列)����。

其中一種可能不合理的方法是使用RC濾波器減慢邊沿�����,從而消除高頻成分���。甚至可以使用正弦波作為時(shí)鐘源���,同時(shí)等待具有50Ω走線和端接的新PCB��。盡管轉(zhuǎn)換是相對(duì)漸進(jìn)的���,并且占空比 可能因數(shù)字輸入遲滯而偏斜,但這將減少抖動(dòng)的反射分量�。

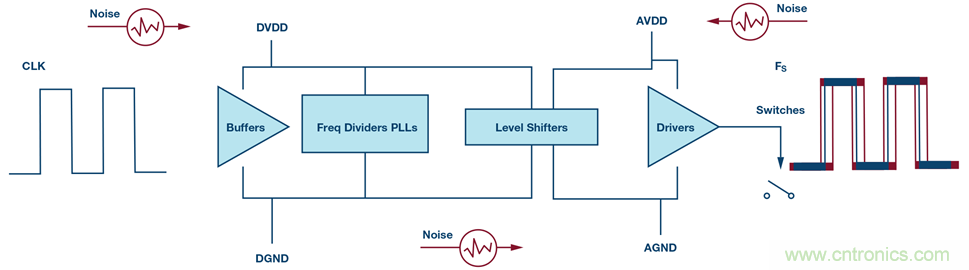

電源噪聲

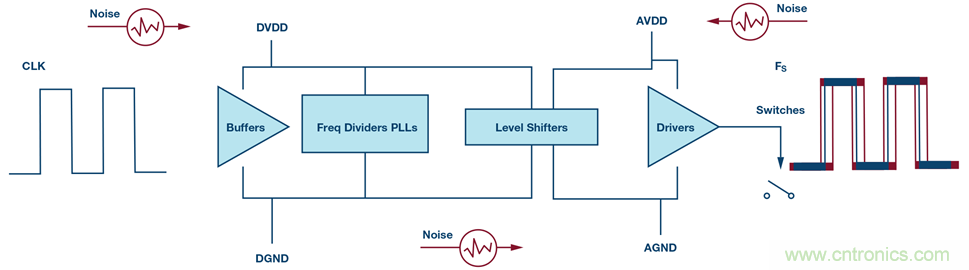

數(shù)字時(shí)鐘可以在將邊沿傳送到采樣開關(guān)之前,通過各種緩沖器和/或電平移位器在ADC內(nèi)部路由���。如果ADC具有模擬電源引腳����,采用的電平移位器將成為抖動(dòng)源����。通常,芯片的模擬端將具有高電壓器件�,并具有更長的壓擺時(shí)間,因此抖動(dòng)靈敏度會(huì)提高���。一些設(shè)計(jì)精良的器件在板上分離更多的模擬電源給時(shí)鐘和線性電路���。

圖 11. 采樣時(shí)間受到DVDD����、AVDD 以及AGND 和 DGND之間不同電源域引入的噪聲干擾

解耦電容:找對(duì)產(chǎn)品

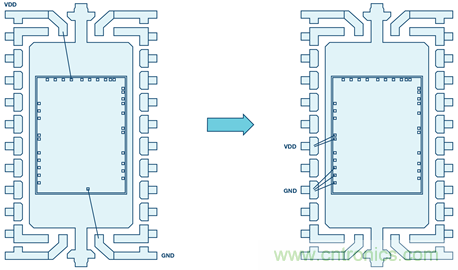

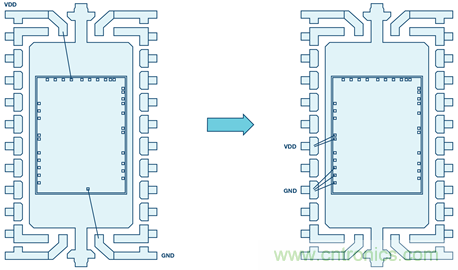

由電源噪聲引起的抖動(dòng)將通過去耦電路減小或放大����。一些∑-Δ調(diào) 制器將在模擬和數(shù)字電路中進(jìn)行大量數(shù)字活動(dòng)����。這可能導(dǎo)致與 信號(hào)和數(shù)字?jǐn)?shù)據(jù)之間干擾有關(guān)的非特征性雜散。高頻電荷傳輸 應(yīng)限制在器件附近的短環(huán)路���。為了適應(yīng)最短的接線����,優(yōu)秀的設(shè) 計(jì)沿著芯片的細(xì)長側(cè)使用中心引腳����。這些限制不是放大器和低 頻芯片的常見問題,它們可以在角上有VDD和VSS引腳���,如圖12的左側(cè)所示��。PCB設(shè)計(jì)應(yīng)充分利用這些功能�,并在引腳附近設(shè)置優(yōu)質(zhì)電容。

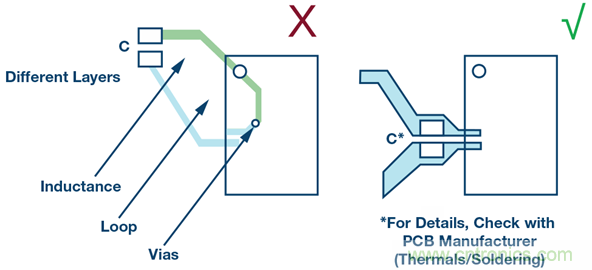

圖12. 線性電路(左)和時(shí)鐘電路(右)的供電方案��。

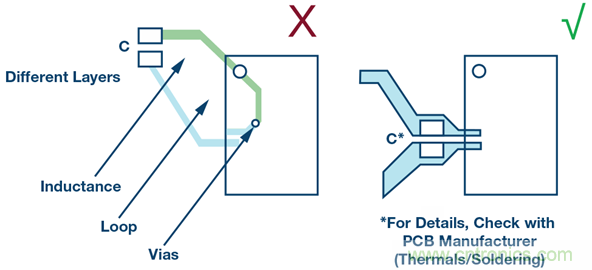

圖13.解耦電容降低抖動(dòng)的錯(cuò)誤(左)和正確(右)位置�。

時(shí)間分頻器和時(shí)鐘信號(hào)隔離器

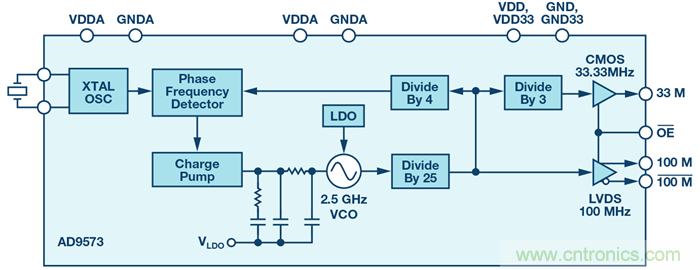

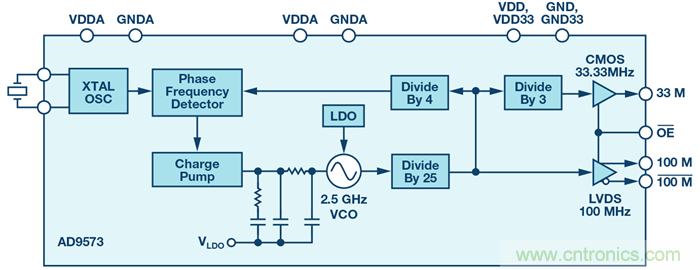

更快的時(shí)鐘具有更少的抖動(dòng),因此如果功率限制允許�����,在外部或內(nèi)部使用分頻器來提供所需的采樣時(shí)鐘會(huì)有所改善�。在設(shè)計(jì)具有隔離器的系統(tǒng)時(shí),請(qǐng)檢查其脈沖寬度���。如果占空比欠佳��,則偏斜會(huì)干擾模擬性能�,在極端情況下�����,可能會(huì)鎖定IC的數(shù)字端����。在精密ADC中,可能不需要光纖時(shí)鐘,但使用更高的頻率可以提供最后一位性能���。在圖14中�����,AD9573在內(nèi)部使用2.5GHz�����,出于相同的原因提供全部33MHz和100MHz����。如果ADC之間不需要精確同步���,則晶振電路可能具有極魯棒的單數(shù)字與抖動(dòng)性能。對(duì)于精密ADC��,晶體放大器在100 kHz輸入時(shí)轉(zhuǎn)換為優(yōu)于22位的性能�����。這種性能很難被超越��,并解釋了為什么XTAL振蕩器在可預(yù)見的未來仍會(huì)使用��。

圖14.AD9573的詳細(xì)功能框圖。

來自其他信號(hào)源的串?dāng)_

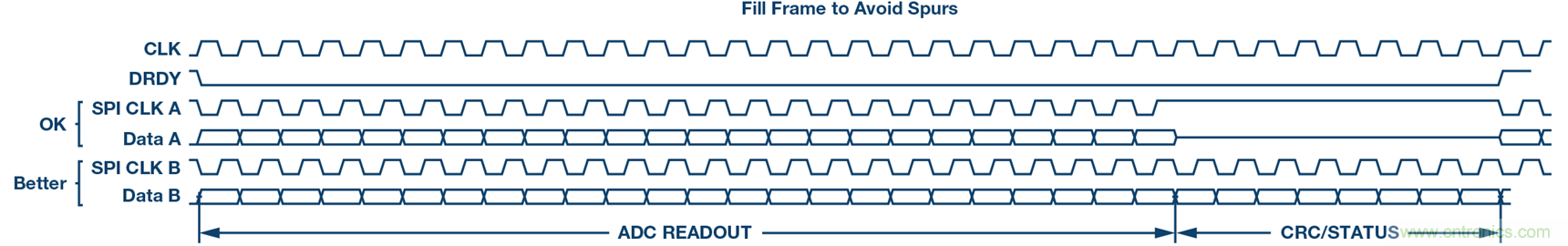

另一個(gè)抖動(dòng)源與源自外部線路的時(shí)鐘干擾有關(guān)��。如果時(shí)鐘源在能夠耦合的信號(hào)附近錯(cuò)誤地路由���,則會(huì)對(duì)性能產(chǎn)生極大影響����。如果干擾源與ADC操作無關(guān)��,并且是隨機(jī)的�����,將極大地增加您的抖動(dòng)預(yù)算�����。如果時(shí)鐘受到與ADC相關(guān)的數(shù)字信號(hào)的污染�,則會(huì)觀察到雜散現(xiàn)象。對(duì)于從ADC���,CLK線路和SPI線路可以是獨(dú)立時(shí)鐘���,但這可能會(huì)在等式9中定義的頻率下導(dǎo)致問題��,并且會(huì)混疊回第一個(gè)奈奎斯特區(qū)����。

建議使用鎖頻SPI和MCLK源�����。即使采用了這種預(yù)防措施���,SPI和MCLK也可能具有與給定時(shí)鐘的脈沖占空比相關(guān)的雜散����。例如���,如果ADC抽取128,并且SPI僅讀取24位��,則會(huì)產(chǎn)生一些創(chuàng)建與特定1/(24t)和1/(104t)測(cè)量相關(guān)的拍頻的風(fēng)險(xiǎn)��。因此���,應(yīng)使MCLK遠(yuǎn)離鎖定的SPI線路以及數(shù)據(jù)線路�。

接口與其他時(shí)鐘

在圖15中,標(biāo)記了各種定時(shí)周期����,這很容易干擾SFDR或?qū)е露秳?dòng)。如果SPI通信未頻鎖到MCLK���,則可能發(fā)生雜散�����。掌握布局技術(shù)是您緩解此問題的最大保障����。頻率表現(xiàn)為混疊下行干擾源��,但也作為拍頻和交調(diào)產(chǎn)物�����。例如�����,如果SPI在16.01 MHz下運(yùn)行,MCLK在16 MHz下運(yùn)行���,則應(yīng)在10 kHz下發(fā)生雜散�����。

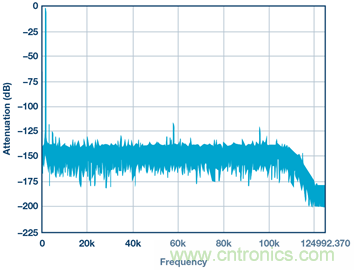

除好的布局之外���,另一種減少雜散的方式是將它們移到相關(guān)頻帶的外部。如果MCLK和SPI可以鎖頻��,則可避免許多干擾���。即便如此���,SPI仍然存在空閑期的問題,導(dǎo)致接地繁忙�����,而這仍然可能造成干擾���。您可以使用對(duì)您有利的接口功能�����。ADC中的接口功能可提供狀態(tài)字節(jié)或循環(huán)冗余校驗(yàn)(CRC)���。這可能提供一種很 好的方法來抑制雜散,并具有這些功能的額外好處���?��?臻e時(shí)鐘,甚至是未使用的CRC字節(jié)��,都有利于均衡地填充數(shù)據(jù)幀��。您可能會(huì)選擇忽略CRC��,而仍然可以通過使用CRC獲得好處����。當(dāng)然,這也意味著數(shù)字線路上需要額外功率�。

圖15. 存在異步通信和時(shí)鐘要求進(jìn)行混合雜散的故障和調(diào)查工作。

圖16. 太靠近開關(guān)模式PSU的MCLK路由����。

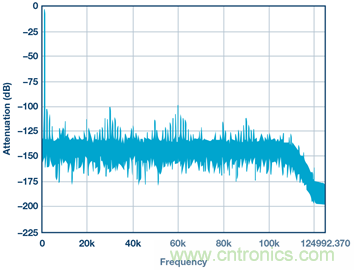

圖17. 具有XTAL放大器和與SPI有關(guān)的雜散的本地源MCLK��。

圖18. 可以使用虛擬CRC或狀態(tài)來改善幀以消除雜散����。

結(jié)論

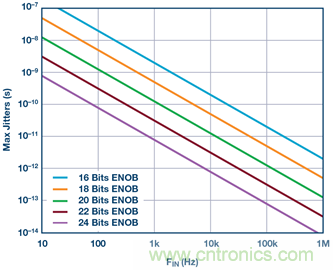

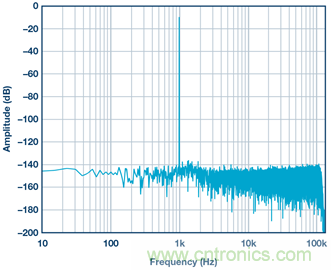

2018年���,ADI發(fā)布了AD7768-1�,這是一款具有低于100μV的偏移和高達(dá)100 kHz的平坦頻率響應(yīng)的高精度ADC����。該ADC已成功應(yīng)用于SFDR超過140 dB的系統(tǒng)設(shè)計(jì)中,事實(shí)證明���,在具有滿量程輸入的音頻帶之外���,抖動(dòng)可忽略不計(jì)。它包含一個(gè)片上RC振蕩器�,能夠提供參考點(diǎn)來調(diào)試受干擾的時(shí)鐘源。這種內(nèi)部RC雖然不能提供低抖動(dòng)�,但可以提供差分方法來發(fā)現(xiàn)雜散源。ADC實(shí)施內(nèi)部開關(guān)電容濾波技術(shù)���,也使用時(shí)鐘分頻器來減輕抗混疊濾波器的壓力��。內(nèi)部時(shí)鐘分頻器可確保穩(wěn)定的性能�,能夠使用通常從隔離器獲取的偏移時(shí)鐘來進(jìn)行操作�����。電源位置非常適合通過內(nèi)部短接合限制外部ESR/ESL效應(yīng)�����。毛刺抑制在時(shí)鐘輸入焊盤中實(shí)現(xiàn)�。應(yīng)用板性能掃描顯示30psrms的抖動(dòng),能夠滿足各種應(yīng)用需求����。如果您需要測(cè)量140+dB的SFDR,AD7768-1能夠幫助您非常迅速地獲取測(cè)量值��,其功耗遠(yuǎn)低于以前的傳統(tǒng)電源軌方式���。

圖19. 具有正確設(shè)計(jì)的PCB和時(shí)鐘電路的AD7768-1的頻譜�����。

參考電路

1 Derek Redmayne, Eric Trelewicz和Alison Smith設(shè)計(jì)說明���。“了解 時(shí)鐘抖動(dòng)對(duì)高速ADC的影響����。”2006年�����。

2 B. E. Boser和B. A. Wooley���。“∑-Δ調(diào)制模數(shù)轉(zhuǎn)換器的設(shè)計(jì)�����。”IEEE J. Solid-State Circ.���,第1298–1308頁,1988年12月���。

3 S. Harris���。“采樣時(shí)鐘抖動(dòng)對(duì)奈奎斯特采樣模數(shù)轉(zhuǎn)換器和過采樣 ∑-Δ型ADC的影響����。” J. Audio Eng. Society�����,第537–542頁��,1990年 7月/8月�����。

4 James A. Chery和W. Martin Snelgrove. “用于高速A/D轉(zhuǎn)換的連續(xù) 時(shí)間∑-Δ調(diào)制器��。” 2002��。

Beex, A. A.和Monique P. Fargues����。“開關(guān)電容系統(tǒng)時(shí)鐘抖動(dòng)分 析�����。”1992年7月。

Markell, Richard����。應(yīng)用筆記。“揭開開關(guān)電容濾波器的神秘面紗: 系統(tǒng)設(shè)計(jì)人員的濾波器綱要����。”1990年3月。

推薦閱讀: